BL1820 低功耗蓝牙应用芯片

---

## ***BL1820***

低功耗蓝牙兼容 & 2.4-GHz 专用 *SOC* 芯片 V1.3

数据手册

---

## 目录

|                                          |     |

|------------------------------------------|-----|

| 版本历史.....                                | 4   |

| 1. BL1820 概览 .....                       | 5   |

| 1.1 简述.....                              | 5   |

| 1.2 芯片特性.....                            | 5   |

| 1.3 系统功能框图.....                          | 7   |

| 1.4 应用.....                              | 8   |

| 2. 脚位图 .....                             | 9   |

| 2.1 BL1820 各型号引脚图 .....                  | 9   |

| 2.2 BL1820 引脚描述 .....                    | 10  |

| 3. MCU 系统 .....                          | 12  |

| 3.1 MCU 调试 .....                         | 12  |

| 3.2 中断向量表 .....                          | 13  |

| 3.4 功能模块寻找表 .....                        | 15  |

| 4. 内存 .....                              | 16  |

| 4.1 内存介绍.....                            | 16  |

| 4.2 内存映射 .....                           | 17  |

| 4.3 APB 寻址空间.....                        | 17  |

| 4.4 AHB 寻址空间.....                        | 18  |

| 5. PMU .....                             | 19  |

| 5.1 电源管理介绍.....                          | 19  |

| 5.2 数字 LDO.....                          | 19  |

| 5.3 POR/BOD.....                         | 20  |

| 6. 外设 .....                              | 20  |

| 6.1 管脚复用 .....                           | 21  |

| 6.2 SDMA .....                           | 22  |

| 6.3 SPI 控制接口 .....                       | 26  |

| 6.4 GPIO .....                           | 44  |

| 6.5 UART .....                           | 50  |

| 6.6 TIMER.....                           | 65  |

| 6.7 GPADC .....                          | 70  |

| 6.8 IIC .....                            | 77  |

| 6.8 WDT (看门狗定时器) .....                   | 88  |

| 6.9 Flash .....                          | 92  |

| 7. 电气特性 (续) .....                        | 93  |

| 7.1 绝对最大额定值 .....                        | 93  |

| 7.2 推荐工作条件 .....                         | 94  |

| 7.3 复位特性 .....                           | 94  |

| 7.4 射频特性 .....                           | 95  |

| 7.2 GPIO 特性 (TA=25°C, VDDIO=3.0 V) ..... | 97  |

| 7.3 通用 ADC 特性 (TA=25°C, VIO=3.3 V) ..... | 98  |

| 7.4 时钟特性 .....                           | 99  |

| 8. 参考设计 .....                            | 101 |

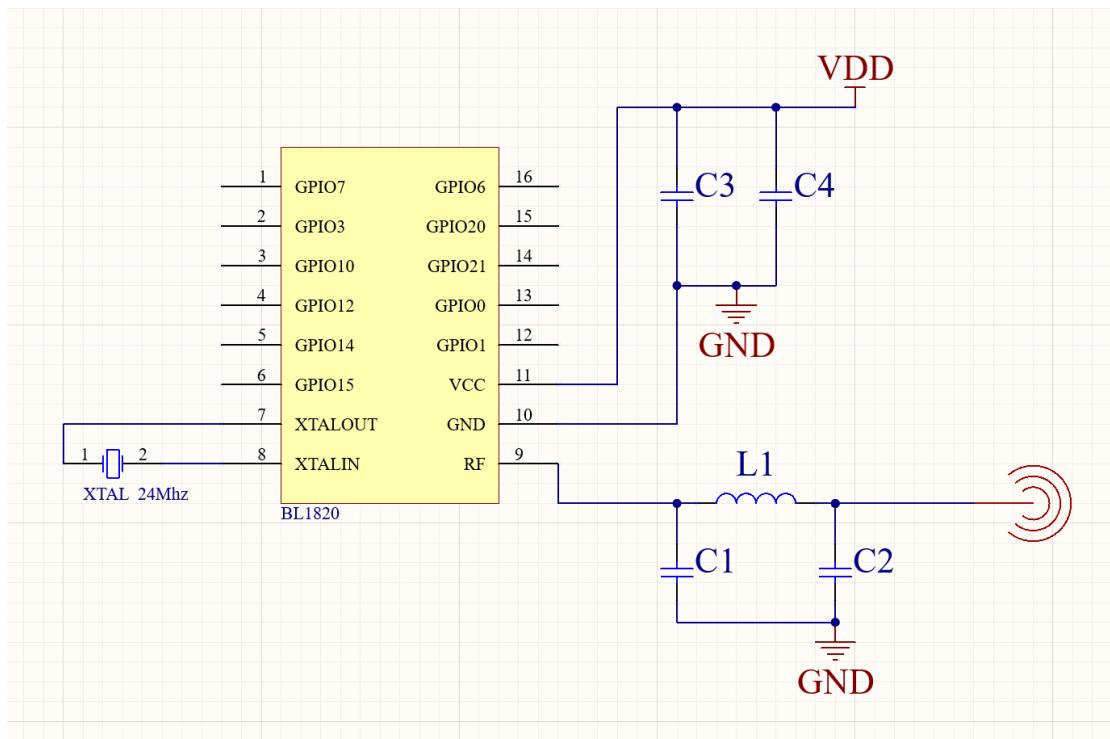

| 8.1 最小系统设计 .....                         | 101 |

| 8.2 典型应用电路示例 (无线传感器节点) .....             | 102 |

| 9. 封装信息 .....                            | 104 |

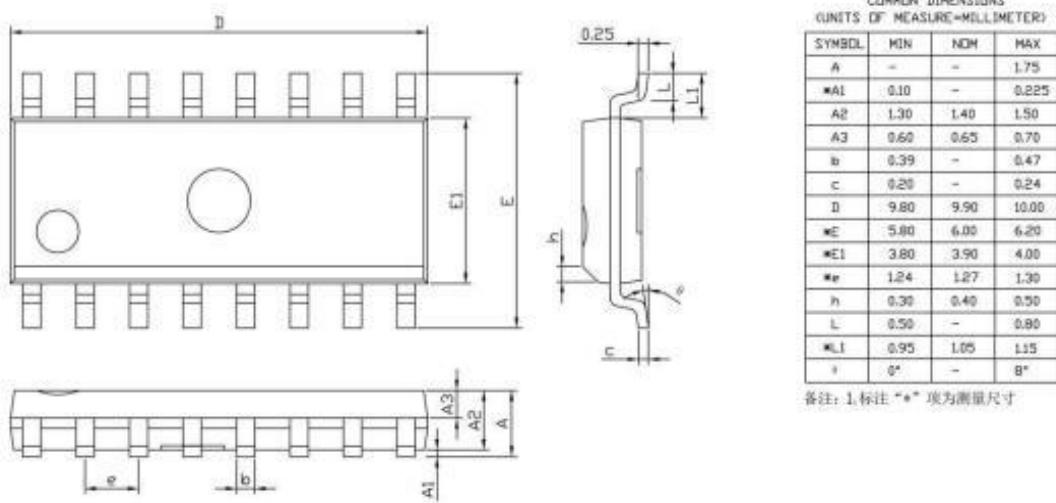

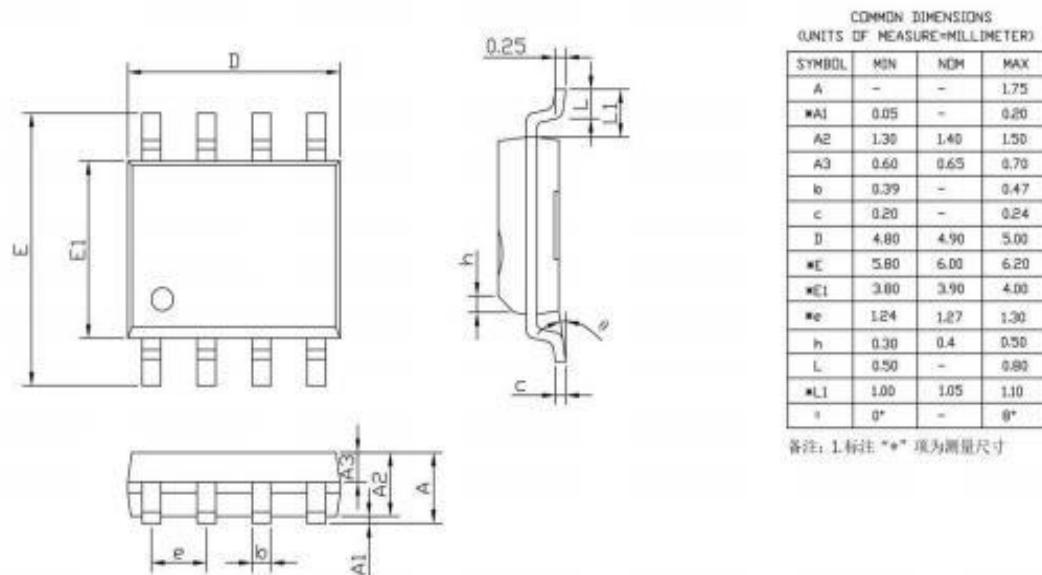

| 9.1 SOP16 封装 (BL1820PPG/FPG) .....       | 104 |

| 9.2 SOP8 封装 (BL1820P8) .....             | 104 |

## BL1820 低功耗蓝牙应用芯片

---

|               |     |

|---------------|-----|

| 10. 缩略语 ..... | 105 |

|---------------|-----|

## 版本历史

| Version | Revision         | Date    | Author | Reviewer |

|---------|------------------|---------|--------|----------|

| V1.08   | Official version | 2024/09 |        |          |

|         |                  |         |        |          |

## 1. BL1820 概览

### 1.1 简述

BL1820 是一款 **16 引脚 RISC-V 核 BLE/2.4G SoC 芯片**，具备高灵敏度（-96dBm@1Mbps）、宽发射功率范围（-10dBm ~ 10dBm）及高集成度（仅需 2~3 颗外部元器件）特性，支持 2.4G 私有协议，可编程通信速率覆盖 125 Kbps/250 Kbps/500 Kbps/1 Mbps/2 Mbps。

芯片支持 2400 MHz ~ 2500 MHz 宽频率输入，低至 60 $\mu$ S 的锁频时间结合专有自动增益控制算法和跳频算法，显著提升 2.4G 频段抗干扰性能，适用于对数据传输稳定性、延迟有高要求的订制类应用；同时针对物联网功耗敏感场景优化，接收/发射峰值电流低，内部集成 T/R 开关和 LDO，无需片外 LDO 退耦电容及射频匹配元件，简化设计并缩小产品尺寸。

### 1.2 芯片特性

#### 1.2.1 射频特性

- 通信速率：支持 125 Kbps/250 Kbps/500 Kbps/1 Mbps/2 Mbps

- 接收灵敏度：-96 dBm @ 1 Mbps

- 发射功率范围：-10 ~ 10 dBm

- RSSI：支持 8-bit RSSI 上报

- 射频匹配：无需外部匹配元件，支持天线直接连接

- 频率范围：2400 MHz ~ 2500 MHz

#### 1.2.2 MCU 子系统

- 内核：

- 32 位 RISC-V 处理器，支持 SWD 调试，最高时钟 48 MHz

- 外设：

- 32 通道 System DMA

- 硬件 AES-128 加密

- 11 个 GPIO（全部支持低功耗唤醒）

- UART × 2（波特率 1200 ~ 2 Mbps，可灵活配置）

- SPI Master × 2（时钟速率最高 24 MHz）、SPI Slave × 1

- IIC × 1 (通信速率最高 1 Mbps)

- 8 路 16bit Timer/PWM

- QSPI × 1

- Watchdog Timer (WDT) × 1

- 32-bit Real-Time Clock (RTC)

- 8 通道 10-bit 3 Mbps ADC

- 温度传感器

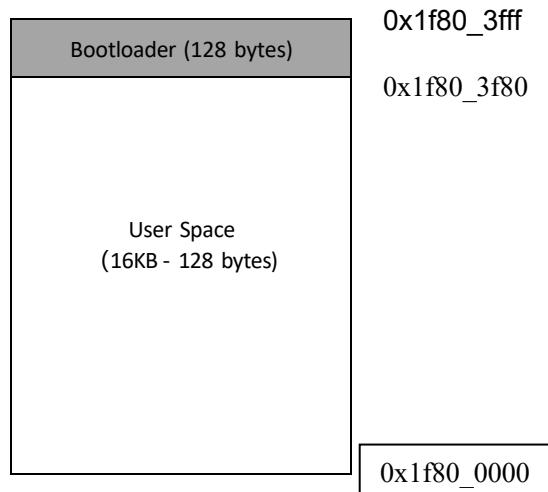

### 1.2.3 存储

- SRAM: 16 KB

- OTP: 16 KB (末尾 128 字节为 bootloader 配置区, 用户不可用)

- Flash: 仅 Flash 版本 (BL1820FPG) 含 256 KB 片上 Flash, 最大支持 64 MB 片外 Flash (可选, 支持 XiP)

### 1.2.4 电源管理

- 供电电压: 1.7 V ~ 3.6 V (集成 LDO)

- 功耗:

- RTC 模式: 3  $\mu$ A (保留 16K RAM)

- 接收峰值功耗: 10 mA

- 发射峰值功耗: 13 mA @ 0 dBm

- 保护机制: 集成 POR/BOR、低电压检测 (LVD) 中断, 支持内部主电源/IO 电压测量

### 1.2.5 时钟

- 内部时钟: 高速 24 MHz RC 振荡器、低速 32 KHz RC 振荡器 (支持所有时钟相互校准)

- 外部时钟: 24 MHz 晶体振荡器 (支持 Crystal trimming)

- 倍频功能: 晶体 24 MHz 时钟可倍频至 48 MHz, 供 CPU 及外设 (QSPI、UART 等) 使用

### 1.2.6 环境与封装

- 工作温度: -40°C ~ +85°C

- 封装: SOP16、SOP8

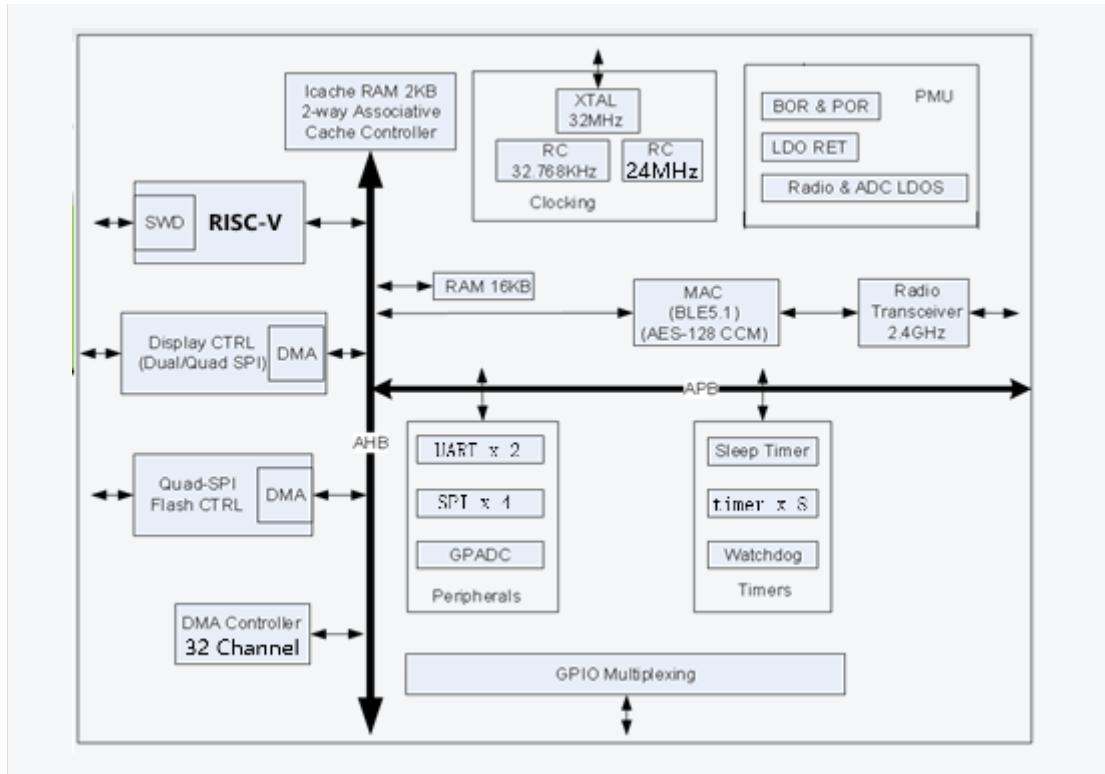

### 1.3 系统功能框图

BL1820 系统架构核心分为 **MCU** 子系统、存储模块、外设模块、电源管理单元、**2.4G 无线模块** 等几大部分，具体框图逻辑如下：

图 1 BL1820 系统框图

## 1.4 应用

BL1820 适用于以下场景：

图 2 BL1824 典型应用

1. **工业控制**：对数据传输延迟、稳定性要求高的订制化工业传感器（如无线温湿度传感器、设备状态监测模块）；

2. **物联网 (IoT)**：功耗敏感型设备（如智能穿戴配件、低功耗无线节点）；

3. **消费电子**：2.4G 私有协议无线连接设备（如无线遥控器、游戏手柄、无线键鼠）；

4. **智能家居**：短距离低功耗无线通信模块（如智能灯具控制、门窗传感器）。

5. **运动健康**

6. **有源标签**

## 2. 脚位图

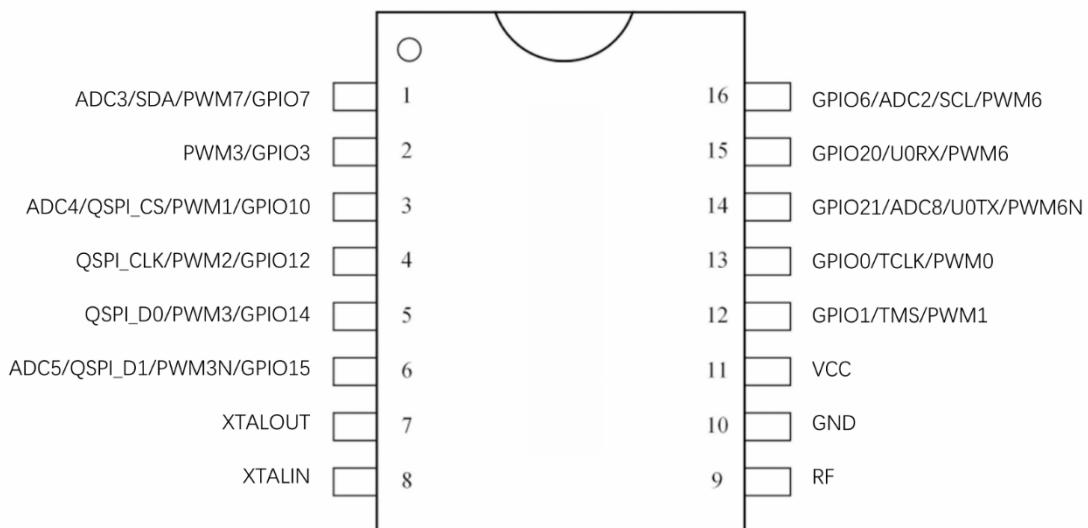

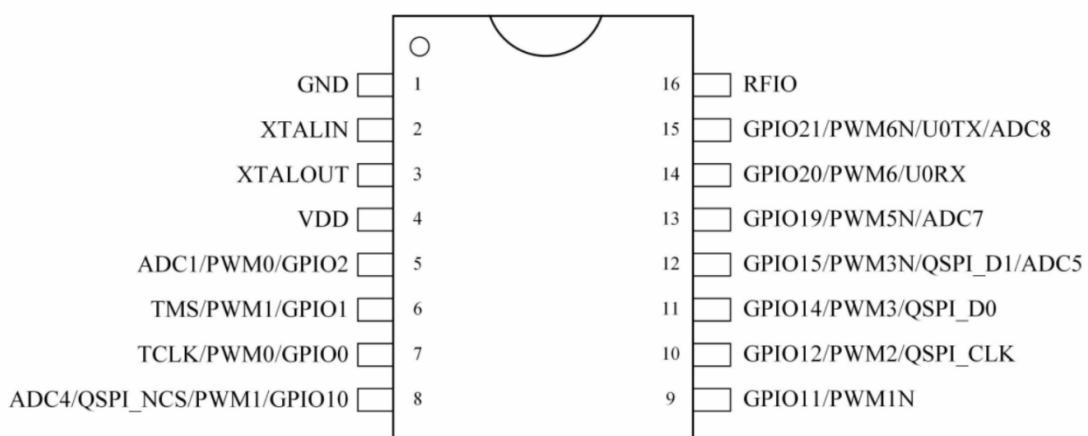

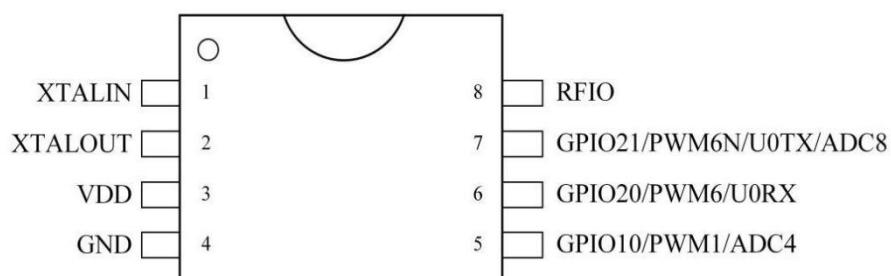

### 2.1 BL1820 各型号引脚图

图 2-1 BL1820PPG

图 2-2 BL1820FPG

图 2-3 BL1820P8

## 2.2 BL1820 引脚描述

| 名称                                    | 1820PP<br>G | 1820FPG | 1820P8 | 类型                       | 描述                                                 |

|---------------------------------------|-------------|---------|--------|--------------------------|----------------------------------------------------|

| <b>ADC3/SDA/PWM7/<br/>GPIO7</b>       | 1           |         |        | AN/<br>I/O/<br>O/I/<br>O | ADC3 模拟输入口 / IIC 数据口 / PWM7 输出口 / 通用输入/输出口         |

| <b>PWM3<br/>GPIO3</b>                 | 2           |         |        | O/I/<br>O                | PWM3 输出口 / 通用输入/输出口                                |

| <b>ADC4/QSPI_CS/PW<br/>M1/GPIO10</b>  | 3           | 8       | 5      | AN/<br>O/O/<br>I/O       | ADC4 模拟输入口 / QSPI 片选信号口 / PWM1 输出口 / 通用输入/输出口      |

| <b>QSPI_CLK/PWM2/G<br/>PIO12</b>      | 4           | 10      |        | O/O/<br>I/O              | QSPI 时钟口 / PWM2 输出口 / 通用输入/输出口                     |

| <b>QSPI_D0/PWM3/GP<br/>IO14</b>       | 5           | 11      |        | I/O/<br>O/I/<br>O        | QSPI 数据输入/输出 0 / PWM3 输出口 / 通用输入/输出口               |

| <b>ADC5/QSPI_D1/PW<br/>M3N/GPIO15</b> | 6           | 12      |        | AN/<br>I/O/<br>O/I/<br>O | ADC5 模拟输入口 / QSPI 数据输入/输出 1 / PWM3N 输出口 / 通用输入/输出口 |

| <b>XTALOUT</b>                        | 7           | 3       | 2      | AN                       | 晶体时钟输出引脚 (外部 24 MHz 晶体输出)                          |

| <b>XTALIN</b>                         | 8           | 2       | 1      | AN                       | 晶体时钟输入引脚 (外部 24 MHz 晶体输入)                          |

| <b>RF_ANT</b>                         | 9           | 16      | 8      | AN                       | 2.4G 射频收发引脚 (直接连接天线, 无需外部匹配)                       |

| <b>GND</b>                            | 10          | 1       | 4      |                          |                                                    |

| <b>VDD</b>                            | 11          | 4       | 3      | P                        | RF 电源和数字电源                                         |

| <b>TMS/PWM1/GPIO1</b>                 | 12          | 6       |        | I/O/<br>O/I/             | JTAG 数据接收口 / PWM1                                  |

## BL1820 低功耗蓝牙应用芯片

|                                    |    |    |   | O                 | 输出口 / 通用输入/输出口                                         |

|------------------------------------|----|----|---|-------------------|--------------------------------------------------------|

| <b>TCLK<br/>/PWM0/GPIO0</b>        | 13 | 7  |   | I<br>O<br>I/O     | JTAG 时钟输入口/ PWM0<br>输出口 /输入/输出口                        |

| <b>ADC8/U0TX/PWM6<br/>N/GPIO21</b> | 14 | 15 | 7 | AN/<br>O/O<br>I/O | ADC8 模拟输入口 / UART0<br>输出口 / PWM6N 互补输出<br>口 / 通用输入/输出口 |

| <b>U0RX/PWM6/GPIO2<br/>0</b>       | 15 | 14 | 6 | I/O/<br>O/I/<br>O | UART0 接收口 / PWM6 输<br>出口 / 通用输入/输出口                    |

| <b>SCL/PWM6/GPIO6</b>              | 16 |    |   | I/O/<br>O/I/<br>O | IIC 时钟口 / PWM6 输出口 /<br>通用输入/输出口                       |

| <b>ADC7 /PWM5N /<br/>GPIO19</b>    |    | 13 |   | AN<br>O<br>I/O    | ADC7 输入口 /PWM5N 输<br>出口/输入/输出口                         |

| <b>PWM1N/GPIO11</b>                |    | 9  |   | O/I/<br>O         | PWM1N 互补输出口 / 通用<br>输入/输出口                             |

| <b>ADC1/PWM0/GPIO2</b>             |    | 5  |   | AN/<br>O/I/<br>O  | ADC1 模拟输入口 / PWM0<br>输出口 / 通用输入/输出口                    |

注：类型缩写说明——I=输入， O=输出， I/O=输入/输出， P=电源， AN=模拟输入/输出。

### 2.3 端口复用功能说明

| IO    | Func1      | Func2    | Func3      | Func4     | Func5      | Func7   |

|-------|------------|----------|------------|-----------|------------|---------|

| GPIO0 | JTAG_TCLK  | IIC0_SCL | SPIM0_NCS  | UART0_CTS | SPIS0_NCS  | PWM_0_P |

| GPIO1 | JTAG_TMS   | IIC0_SDA | SPIM0_SCK  | UART0_RTS | SPIS0_SCK  | PWM_1_P |

| GPIO2 | JTAG_TRSTB | UART0_RX | SPIM0_MOSI | UART1_CTS | SPIS0_MISO | PWM_2_P |

| IO     | Func1    | Func2    | Func3      | Func4      | Func5      | Func7   |

|--------|----------|----------|------------|------------|------------|---------|

| GPIO3  | Reserved | UART0 TX | SPIM0 MISO | UART1 RTS  | SPIS0 MOSI | PWM_3_P |

| GPIO4  | QSPI_NCS | UART1_RX | SPIM1_SCK  | SPIS0_NCS  | UART0_RX   | PWM_4_P |

| GPIO5  | QSPI_D3  | UART1_TX | SPIM1_NCS  | SPIS0_SCK  | UART0_TX   | PWM_5_P |

| GPIO6  | QSPI_CLK | IIC0_SCL | SPIM1_MOSI | SPIS0_MOSI | UART1_RX   | PWM_6_P |

| GPIO7  | QSPI_D2  | IIC0_SDA | SPIM1_MISO | SPIS0_MISO | UART1_TX   | PWM_7_P |

| GPIO8  | QSPI_D0  | UART0_RX | SPIM0_NCS  | UART1_CTS  | SPIS0_NCS  | PWM_0_P |

| GPIO9  | QSPI_D1  | UART0_TX | SPIM0_SCK  | UART1_RTS  | SPIS0_SCK  | PWM_0_N |

| GPIO10 | QSPI_NCS | UART1_RX | SPIM0_MOSI | UART0_CTS  | SPIS0_MOSI | PWM_1_P |

| GPIO11 | QSPI_D3  | UART1_TX | SPIM0_MISO | UART0_RTS  | SPIS0_MISO | PWM_1_N |

| GPIO12 | QSPI_CLK | IIC0_SCL | SPIM1_SCK  | SPIS0_NCS  | UART0_RX   | PWM_2_P |

| GPIO13 | QSPI_D2  | IIC0_SDA | SPIM1_NCS  | SPIS0_SCK  | UART0_TX   | PWM_2_N |

| GPIO14 | QSPI_D0  | UART0_RX | SPIM1_MOSI | SPIS0_MOSI | UART1_RX   | PWM_3_P |

| GPIO15 | QSPI_D1  | UART0_TX | SPIM1_MISO | SPIS0_MISO | UART1_TX   | PWM_3_N |

| GPIO16 | QSPI_NCS | UART1_RX | SPIM0_NCS  | IIC0_SCL   | SPIS0_NCS  | PWM_4_P |

| GPIO17 | QSPI_D3  | UART1_TX | SPIM0_SCK  | IIC0_SDA   | SPIS0_SCK  | PWM_4_N |

| GPIO18 | QSPI_CLK | IIC0_SCL | SPIM0_MOSI | UART1_CTS  | SPIS0_MOSI | PWM_5_P |

| GPIO19 | QSPI_D2  | IIC0_SDA | SPIM0_MISO | UART1_RTS  | SPIS0_MISO | PWM_5_N |

| GPIO20 | QSPI_D0  | UART0_RX | SPIM1_SCK  | SPIS0_NCS  | IIC0_SCL   | PWM_6_P |

| GPIO21 | QSPI_D1  | UART0_TX | SPIM1_NCS  | SPIS0_SCK  | IIC0_SDA   | PWM_6_N |

| GPIO22 | IIC0_SCL | UART1_RX | SPIM1_MOSI | SPIS0_MOSI | QSPI_CLK   | PWM_7_P |

| GPIO23 | IIC0_SDA | UART1_TX | SPIM1_MISO | SPIS0_MISO | QSPI_NCS   | PWM_7_N |

### 3. MCU 系统

#### 3.1 MCU 调试

BL1820 的 MCU (32 位 RISC-V 核) 支持 SWD (Serial Wire Debug) 两线调试接口，调

试引脚复用 GPIO0 (TCLK) 和 GPIO1 (TMS) , 具体功能如下:

- TCLK (GPIO0) : 调试时钟信号, 由调试器输出;

- TMS (GPIO1) : 调试模式选择信号, 双向传输, 用于调试命令与数据交互;

- 调试功能: 支持程序下载、断点调试、寄存器读写、内存访问, 兼容 RISC-V debug 架构。

## 3.2 中断向量表

BL1820 中断控制器兼容 RISC-V CLIC 标准, 支持中断嵌套, 中断向量表如下:

| Number | IRQ         | Bit | Description     |

|--------|-------------|-----|-----------------|

| 0~2    | N/A         | -   | 保留              |

| 3      | SOFT_IRQ    | 1   | 软件中断            |

| 4~6    | N/A         | -   | 保留              |

| 7      | TIMER_IRQ   | 1   | 定时器全局中断         |

| 8~15   | N/A         | -   | 保留              |

| 16     | WDT         | 1   | 看门狗定时器中断        |

| 17     | N/A         | -   | 保留              |

| 18     | RADIO_CTRL  | 1   | 2.4G 控制器中断      |

| 19     | RADIO_TIMER | 1   | 2.4G 定时器中断      |

| 20     | RADIO_PTMR  | 1   | 2.4G 周期定时器中断    |

| 21~22  | N/A         | -   | 保留              |

| 23     | GPADC       | 1   | 通用 ADC 中断       |

| 24     | UART_0      | 1   | UART0 中断        |

| 25     | UART_1      | 1   | UART1 中断        |

| 26     | SPIM_0      | 1   | SPI Master 0 中断 |

## BL1820 低功耗蓝牙应用芯片

| Number | IRQ     | Bit | Description     |

|--------|---------|-----|-----------------|

| 27     | SPIM_1  | 1   | SPI Master 1 中断 |

| 28     | IIC     | 1   | IIC 中断          |

| 29     | N/A     | -   | 保留              |

| 30     | SPIS    | 1   | SPI Slave 中断    |

| 31     | N/A     | -   | 保留              |

| 32     | GPIO    | 1   | GPIO 全局中断       |

| 33     | QDEC    | 1   | 正交解码器中断         |

| 34     | AES     | 1   | AES 加密模块中断      |

| 35     | CAP     | 1   | 捕获模块中断          |

| 36     | CLKCAL  | 1   | 时钟校准中断          |

| 37     | RTC     | 1   | 实时时钟中断          |

| 38     | SDMA    | 1   | SDMA 控制器中断      |

| 39     | LVD     | 1   | 低电压检测中断         |

| 40     | TIMER_0 | 1   | 定时器 0 中断        |

| 41     | TIMER_1 | 1   | 定时器 1 中断        |

| 42     | TIMER_2 | 1   | 定时器 2 中断        |

| 43     | TIMER_3 | 1   | 定时器 3 中断        |

| 44     | TIMER_4 | 1   | 定时器 4 中断        |

| 45     | TIMER_5 | 1   | 定时器 5 中断        |

| 46     | TIMER_6 | 1   | 定时器 6 中断        |

| Number | IRQ     | Bit | Description |

|--------|---------|-----|-------------|

| 47     | TIMER_7 | 1   | 定时器 7 中断    |

### 3.4 功能模块寻找表

BL1820 各功能模块的基地址如下，便于软件访问与配置：

| BaseAddress | Module  | Description                |

|-------------|---------|----------------------------|

| 0x40000000  | SYS_REG | 系统控制寄存器                    |

| 0x41008000  | TIMER   | 定时器模块 (Timer0~Timer7)      |

| 0x42000000  | 2.4G_RF | 2.4G 射频模块                  |

| 0x40010000  | GPIO    | GPIO 控制器                   |

| 0x41001000  | UART0   | 通用异步收发器 0                  |

| 0x41002000  | UART1   | 通用异步收发器 1                  |

| 0x40040000  | GPADC   | 通用 ADC 模块                  |

| 0x41003000  | SPI_M0  | SPI Master 0               |

| 0x41004000  | SPI_M1  | SPI Master 1               |

| 0x41007000  | SPIS    | SPI Slave                  |

| 0x41005000  | IIC     | IIC 控制器                    |

| 0x1F800000  | OTP     | 一次性可编程存储器 (16KB)           |

| 0x20000000  | SRAM    | 静态随机存储器 (16KB)             |

| 0x10000000  | Flash   | 片外 Flash (最大 64MB, 支持 XiP) |

## 4. 内存

### 4.1 内存介绍

BL1820 的存储系统包含片内存储器（**SRAM**、**OTP**）和片外扩展存储器（**Flash**），具体配置如下：

1. **SRAM**: 总容量 16 KB，分为 3 个独立区块，每块可单独设置 Retention（低功耗模式下数据保持）：

- RAM Block 0: 4 KB

- RAM Block 1: 4 KB

- RAM Block 2: 8 KB

2. **OTP**: 总容量 16 KB，地址范围 0x1F80\_0000 ~ 0x1F803FFF，其中末尾 128 字节（0x1F803F80 ~ 0x1F803FFF）为 bootloader 配置区，用户不可访问，剩余 16 KB - 128 B 为用户可用区；

图 4-1 OTP 存储器映射

3. **Flash**:

- 片上 Flash: 仅 BL1820FPG 型号集成 256 KB，地址范围 0x10000000 ~ 0x10040000；

- 片外 Flash: 最大支持 64 MB，支持 XiP (Execute-in-Place，直接从 Flash 执行程序)，通过 QSPI 接口访问。

## 4.2 内存映射

BL1820 的内存地址空间分布如下（32位地址）：

| Address Range            | Size  | Module           | Description                       |

|--------------------------|-------|------------------|-----------------------------------|

| 0x00000000 ~ 0x00007FFF  | 32 KB | ROM              | 只读存储器（存放 bootloader）              |

| 0x1F800000 ~ 0x1F803FFF  | 16 KB | OTP              | 一次性可编程存储器（用户区+boot 区）             |

| 0x20000000 ~ 0x20003FFF  | 16 KB | SRAM             | 静态随机存储器<br>(Block0+Block1+Block2) |

| 0x40000000 ~ 0x5FFFFFFF  | 0.5GB | Peripherals      | 外设寄存器区（GPIO、UART、SPI 等）           |

| 0x40000000 ~ 0x40FFFFFF  | 64 MB | APB1 Peripherals | APB1 总线外设（Timer、SPIS 等）           |

| 0x42000000 ~ 0x42FFFFFF  | 12 KB | 2.4G Radio/Modem | 2.4G 射频/调制解调器寄存器                  |

| 0x1000_0000 ~ 0x13FFFFFF | 64 MB | External Flash   | 片外 Flash（支持 XiP）                  |

| 0x41000000 ~ 0x41FFFFFF  | 64 MB | AHB1 Peripherals | AHB1 总线外设（CPU、RAM 等）              |

| 0x40000000 ~ 0x4000FFFF  | 64 KB | System Control   | 系统控制寄存器（复位、时钟等）                   |

## 4.3 APB 寻址空间

APB 总线（Advanced Peripheral Bus）用于连接低速外设，BL1820 的 APB 寻址空间细分如下：

| Address Range           | Size | Module | Description               |

|-------------------------|------|--------|---------------------------|

| 0x41000000 ~ 0x41001FFF | 4 KB | UART0  | UART0 相关寄存器               |

| 0x41002000 ~ 0x41002FFF | 4 KB | UART1  | UART1 相关寄存器               |

| 0x41003000 ~ 0x41003FFF | 4 KB | SPIM0  | SPI Master 0 相关寄存器        |

| 0x41004000 ~ 0x41004FFF | 4 KB | SPIM1  | SPI Master 1 相关寄存器        |

| 0x41005000 ~ 0x41006FFF | 4 KB | IIC    | IIC 相关寄存器                 |

| 0x41007000 ~ 0x41007FFF | 4 KB | SPIS   | SPI Slave 相关寄存器           |

| 0x41008000 ~ 0x41008FFF | 4 KB | TIMER  | 定时器 (Timer0~Timer7) 相关寄存器 |

## 4.4 AHB 寻址空间

AHB 总线 (Advanced Peripheral Bus) 用于连接高速外设, BL1820 的 AHB 寻址空间细分如下:

| Address Range           | Size  | Module  | Description |

|-------------------------|-------|---------|-------------|

| 0x40000000 ~ 0x4000FFFF | 64 KB | SYS_REG | SYS 相关寄存器   |

| 0x40010000 ~ 0x4001FFFF | 64 KB | GPIO    | GPIO 相关寄存器  |

| 0x40020000 ~ 0x4002FFFF | 64 KB | QDEC    | QDEC 相关寄存器  |

| 0x40030000 ~ 0x4003FFFF | 64 KB | AES     | AES 相关寄存器   |

| 0x40040000 ~ 0x4007FFFF | 64 KB | GPADC   | 通用 ADC 寄存器  |

| Address Range           | Size  | Module | Description   |

|-------------------------|-------|--------|---------------|

| 0x40080000 ~ 0x4008FFFF | 64 KB | LPM    | SPI Slave 寄存器 |

## 5. PMU

### 5.1 电源管理介绍

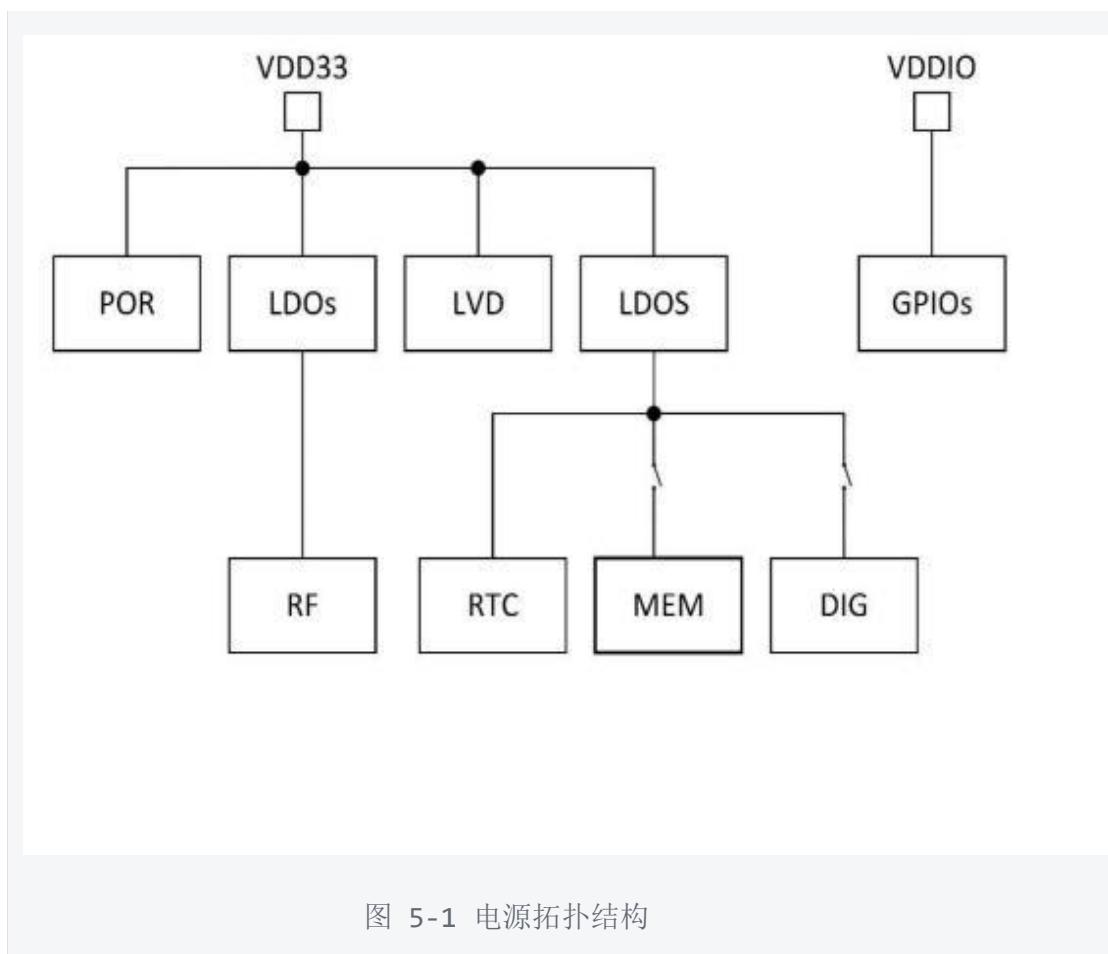

BL1820 的电源管理单元 (PMU) 负责为芯片各模块提供稳定供电，并实现低功耗控制，电源拓扑如下：

- LDO 分类**：包含 RF 专用 LDO、数字电路 LDO、IO LDO，分别为 2.4G 射频模块、MCU/外设、GPIO 提供稳定电压；

- 功耗控制**：支持多档功耗模式（RTC 模式、休眠模式、正常工作模式），通过关闭闲置模块时钟/电源降低功耗。

### 5.2 数字 LDO

数字 LDO 为 MCU 内核、SRAM、数字外设（UART、SPI 等）提供供电，技术参数如下：

| Parameter | Symbol   | Condition | Min | Typ | Max | Unit |

|-----------|----------|-----------|-----|-----|-----|------|

| 输入电压范围    | VIN      | 来自 VDD 电源 | 1.7 |     | 3.9 | V    |

| 输出电压范围    | VOUT     | 数字内核供电    | 1.0 | 1.1 | 1.2 | V    |

| 输出电流能力    | IOUT_MAX | 满载时       | -   | 50  | 100 | mA   |

## 5.3 POR/BOD

### 5.3.1 上电复位 (POR)

- 功能：**电源电压从 0 上升时，当 VDD 达到 VPOR（1.7 V 典型值）后，POR 模块延迟 TPOR（20 ms 典型值）后释放复位，确保芯片稳定启动；若 VDD 下降至 VPDR（1.2 V 典型值）以下，立即触发复位；

- 应用：**芯片上电初始化、电源电压骤降保护。

### 5.3.2 低电压检测 (LVD)

- 功能：**实时监测 VDD/VDDIO 电压，当电压低于设定阈值（可配置，默认 1.6 V）时，可触发中断（通知 CPU 处理）或直接复位（防止芯片异常工作）；

- 特性：**支持内部主电源（VDD）和 IO 电源（VDDIO）分别检测，中断可独立使能/禁用，复位仅影响非 AON（Always-On）区域。

## 6. 外设

## 6.1 管脚复用

BL1820 的内部有 24 个 GPIO (GPIO0~GPIO23) 均支持多外设复用，通过寄存器 PIN\_MUX\_CTRL\_1~PIN\_MUX\_CTRL\_5 配置，部分常用管脚复用表如下：

| IO     | Func1       | Func2    | Func3      | Func4      | Func5      | Func7   |

|--------|-------------|----------|------------|------------|------------|---------|

| GPIO0  | JTAG_TCLK   | IIC0_SCL | SPIM0_NCS  | UART0_CTS  | SPIS0_NCS  | PWM_0_P |

| GPIO1  | JTAG_TMS    | IIC0_SDA | SPIM0_SCK  | UART0_RTS  | SPIS0_SCK  | PWM_1_P |

| GPIO2  | JTAG_TRST_B | UART0_RX | SPIM0_MOSI | UART1_CTS  | SPIS0_MISO | PWM_2_P |

| GPIO3  | Reserved    | UART0_TX | SPIM0_MISO | UART1_RTS  | SPIS0_MOSI | PWM_3_P |

| GPIO4  | QSPI_NCS    | UART1_RX | SPIM1_SCK  | SPIS0_NCS  | UART0_RX   | PWM_4_P |

| GPIO5  | QSPI_D3     | UART1_TX | SPIM1_NCS  | SPIS0_SCK  | UART0_TX   | PWM_5_P |

| GPIO6  | QSPI_CLK    | IIC0_SCL | SPIM1_MOSI | SPIS0_MOSI | UART1_RX   | PWM_6_P |

| GPIO7  | QSPI_D2     | IIC0_SDA | SPIM1_MISO | SPIS0_MISO | UART1_TX   | PWM_7_P |

| GPIO8  | QSPI_D0     | UART0_RX | SPIM0_NCS  | UART1_CTS  | SPIS0_NCS  | PWM_0_P |

| GPIO9  | QSPI_D1     | UART0_TX | SPIM0_SCK  | UART1_RTS  | SPIS0_SCK  | PWM_0_N |

| GPIO10 | QSPI_NCS    | UART1_RX | SPIM0_MOSI | UART0_CTS  | SPIS0_MOSI | PWM_1_P |

| GPIO11 | QSPI_D3     | UART1_TX | SPIM0_MISO | UART0_RTS  | SPIS0_MISO | PWM_1_N |

| GPIO12 | QSPI_CLK    | IIC0_SCL | SPIM1_SCK  | SPIS0_NCS  | UART0_RX   | PWM_2_P |

| IO     | Func1   | Func2    | Func3       | Func4       | Func5    | Func7   |

|--------|---------|----------|-------------|-------------|----------|---------|

|        |         |          | K           | S           |          | P       |

| GPIO13 | QSPI_D2 | IIC0_SDA | SPIM1_NC_S  | SPIS0_SC_K  | UART0_TX | PWM_2_N |

| GPIO14 | QSPI_D0 | UART0_RX | SPIM1_MO_SI | SPIS0_MO_SI | UART1_RX | PWM_3_P |

| GPIO15 | QSPI_D1 | UART0_TX | SPIM1_MISO  | SPIS0_MISO  | UART1_TX | PWM_3_N |

### 6.1.1 管脚复用寄存器映射

| Address    | Name       | Description                         |

|------------|------------|-------------------------------------|

| 0x40010204 | GPIO_CFG_1 | GPIO0~GPIO3 复用配置 (每 GPIO 占 8 bit)   |

| 0x40010208 | GPIO_CFG_2 | GPIO4~GPIO7 复用配置 (每 GPIO 占 8 bit)   |

| 0x4001020C | GPIO_CFG_3 | GPIO8~GPIO11 复用配置 (每 GPIO 占 8 bit)  |

| 0x40010210 | GPIO_CFG_4 | GPIO12~GPIO15 复用配置 (每 GPIO 占 8 bit) |

| 0x40010214 | GPIO_CFG_5 | GPIO16~GPIO18 复用配置 (每 GPIO 占 8 bit) |

寄存器配置规则：每个 GPIO 的复用控制位为 6 bit（如 GPIO0 对应 PIN\_MUX\_CTRL\_1[5:0]），不同值对应不同功能（参考上表 Func1~Func7），默认值为 0（GPIO 模式）。

## 6.2 SDMA

## 6.2.1 简介

SDMA (Simple Direct Memory Access) 将数据从一个地址空间搬移到另一个地址空间而不需要 CPU 参与，提供在外设和存储器之间或者存储器 和存储器之间的高速数据传输。当 CPU 初始化这个传输动作，传输动作本身是由 DMA 控制器来实现和完成。DMA 传输方式无需 CPU 直接控制传输，也没有中断处理方式那样保留现场和恢复现场过程，通过硬件为内存与外设开辟一条直接传输数据的通道，使得 CPU 的效率大大提高。

## 6.2.2 主要特性

- 通道数量：32 路独立通道，支持优先级配置（高/低两档）；

- 传输宽度：8-bit、32-bit；

- 传输模式：标准模式、FIFO 模式、CMD 模式；

- 地址模式：两种地址类型，即外设、存储器； 两种地址变化模式：固定、自增。

- 寻址范围：32 位全空间（最大传输 64 KB）；

- 中断：每路通道传输完成可独立触发中断。

## 6.2.3 功能描述

### [6.2.3.1] 传输模式

**标准模式：** SDMA 标准模式是从源地址区域向目的地址区域搬移数据内容，搬移过程中源区域和 目的区域能内地址线性增加，或者不增加，源和目的侧可以单独设置。标准模式搬移指定 大小数据内容后，完成通道任务。数据搬移单位由配置域 DMA\_WORD\_EN 进行设置，进行 8 位字节搬移或 32 位字进行搬移。数据搬移长度由配置域 NUM\_BYTES 设置，最大搬 移大小为 64KB，当 DMA\_WORD\_EN 为“1”时，NUM\_BYTES 最低两位必须是 0，以保证 32 位字对齐。

**CMD 模式：** CMD 模式传输除了在原有标准模式传输的基础上，会在标准传输前或传输后额外执行 一条 CMD 指令。DMA 配置域 CMD\_PRE\_EN 用于决定 CMD 执行先后顺序，该位为 1 时，先执行 CMD 指令，再执行 DMA 传输；该位为 0 时，限制性 DMA 传输，再执行 CMD 操作。CMD 写入内容由配置域 CMD\_WAR 确定，该位为 0 时，为 Mask 写模式，直接向 CMD\_ADDR 写入 (CMD\_WDATA&(~CMD\_MASK))。该位为 1 时，为“读改写”模式，首先读取 CMD\_ADDR，并存储至 CMD\_RDATA，再向 CMD\_ADDR 写入(CMD\_RDATA& CMD\_MASK) | (CMD\_WDATA &(~CMD\_MASK))。

**FIFO 模式：** FIFO 模式和标准模式传输类似，不同的是源起始地址与目标地址在 FIFO 模式下递增 到 FIFO\_SIZE 边界时，源起始地址或目的起始地址。FIFO 模式由配置域 FIFO\_MODE<1:0> 进行配置：

- Bit[1]: 源起始地址 FIFO 模式使能开关

- Bit[0]: 目标地址 FIFO 模式使能开关。

### [6.2.3.2] SDMA 中断

SDMA 32 个任务均可独立产生中断，通过任务描述符 DMA\_TASK\_CFG0<31> INT\_EN 控制中断，当对应任务的 INT\_EN 配置为“1”时，当任务传输完成后，将触发产生 SDMA 中断。SDMA 每个任务的中断状态存储在寄存器 SDMA\_INT\_STATUS<31:0>中，SDMA 中断服务程序应先读取 SDMA\_INT\_STATUS<31:0>，确定中断来自哪一个 SDMA 任务，从而选择对应的中断处理程序，中断处理完成后，通过寄存器 SDMA\_INT\_CLEAR<31:0>清除对应的中断标志位。

- **触发条件：**通道传输完成（需通过 DMA\_TASK\_CFG0[31]使能中断）；

- **状态查询：**中断状态存储于 SDMA\_INT\_STATUS[31:0]，每 bit 对应一路通道；

- **中断清除：**通过 SDMA\_INT\_CLEAR[31:0]写入 1 清除对应通道中断标志。

## 6.2.4 寄存器映射

SDMA 基地址：0x40000000，其他有关 SDMA 的寄存器配置，在此基地址加上相应 的偏移地址。

### 1. SDMA 使能寄存器 ( sdma\_en )

偏移地址：0x110

|         |     |    |

|---------|-----|----|

| sdma_en | [0] | RW |

|---------|-----|----|

SDMA 失能/使能：写 1 使能，写 0 失能。

### 2. SDMA 任务表地址寄存器 ( sdma\_task\_table\_addr )

偏移地址：0x114

|                      |        |    |

|----------------------|--------|----|

| sdma_task_table_addr | [31:0] | RW |

|----------------------|--------|----|

32dma 逻辑信道表的起始地址，每个字指向每个信道的任务描述符。

### 3. SDMA 操作寄存器 ( sdma\_action )

偏移地址：0x118

|                  |               |                |

|------------------|---------------|----------------|

| RW               | RW            | RW             |

| [2]              | [1]           | [0]            |

| sdma_task_remove | sdma_task_add | sdma_task_load |

|      |                                                                   |

|------|-------------------------------------------------------------------|

| bit0 | sdma_task_load: 任务装载动作位, 写 1对 sdma_task_val 中被置 1 的通道执行“装载任务”操作   |

| bit1 | sdma_task_add: 任务添加动作位, 写 1对 sdma_task_val 中被置 1 的通道执行“添加任务”操作    |

| bit2 | sdma_task_remove: 任务移除动作位, 写 1对 sdma_task_val 中被置 1 的通道执行“移除任务”操作 |

#### 4. SDMA 任务值寄存器 (sdma\_task\_val)

偏移地址: 0x11C

|                  |        |    |

|------------------|--------|----|

| sdma_task_status | [31:0] | RO |

|------------------|--------|----|

每个逻辑 dma 信道的状态, 1: 通道正在运行, 0: 通道空闲

#### 5. SDMA 任务值寄存器 (sdma\_task\_val)

偏移地址: 0x120

|               |        |    |

|---------------|--------|----|

| sdma_task_val | [31:0] | RW |

|---------------|--------|----|

dma 任务操作通道, 每个比特对应每个 dma 信道。

#### 6. SDMA 中断状态寄存器 (sdma\_int\_status)

偏移地址: 0x124

|                 |        |    |

|-----------------|--------|----|

| sdma_int_status | [31:0] | RO |

|-----------------|--------|----|

DMA 通道中断状态, 1 表示该通道有待处理中断; 0 表示无中断

#### 7. SDMA 中断清除寄存器 (sdma\_int\_clear)

偏移地址: 0x128

|                |        |    |

|----------------|--------|----|

| sdma_int_clear | [31:0] | RW |

|----------------|--------|----|

中断清除寄存器, 对任意位写 1 将立即清除 sdma\_int\_status 中的对应中断标志; 写 0 无影响。

## 6.3 SPI 控制接口

### 6.3.1 简介

串行外设接口（SPI）是同步串行通信协议，BL1820 集成 **2 个 SPI Master (SPIM0/SPIM1)** 和 **1 个 SPI Slave (SPIS)**，支持半/全双工通信，适用于与外部 SPI 设备（如 Flash、传感器、显示屏）的数据交互。

- **SPI Master**: 主动发起通信，提供时钟信号（SCK），控制片选（NCS），适用于主机控制从机的场景；

- **SPI Slave**: 被动响应通信，时钟由 Master 提供，仅在被选中（NCS 有效）时传输数据，适用于从机接收主机指令的场景。

### 6.3.2 SPI Master

#### [6.3.2.1] SPI Master 简介

SPI Master 通过 MOSI（主发从收）、MISO（主收从发）、SCK（时钟）、NCS（片选）4 个引脚与外部从设备通信，支持四线、三线传输模式，最高时钟速率 24 MHz，满足中高速数据传输需求。

#### [6.3.2.2] SPI Master 主要特性

| 特性分类 | 具体参数/功能           |

|------|-------------------|

| 通信模式 | 全双工四线、半双工四线、半双工三线 |

| 帧格式  | 8-bit/16-bit 可选   |

| 特性分类    | 具体参数/功能                                                |

|---------|--------------------------------------------------------|

| 时钟性能    | 最高 24 MHz, 时钟极性 (SCPOL)、相位 (SCPH) 可配置, 支持 4 种 SPI 传输模式 |

| FIFO 缓冲 | 发送/接收 FIFO 深度均为 16 字节, 减少 CPU 中断频率                     |

| 传输控制    | 支持 EEPROM READ 模式 (专为 Flash 读命令设计, 含 3 字节命令帧)          |

| 中断支持    | 发送空、发送溢出、接收满、接收溢出、接收欠流中断, 可独立使能/屏蔽                     |

### [6.3.2.3] SPI Master 功能描述

#### 1. 传输模式

通过 `CTRLR0` 寄存器配置, 支持 4 种传输模式:

- **TX AND RX (全双工)** : 发送数据的同时接收从机反馈数据 (如 SPI Flash 读写) ;

- **TX ONLY (半双工发送)** : 仅通过 MOSI 发送数据, MISO 引脚无效 (如仅写传感器配置) ;

- **RX ONLY (半双工接收)** : 仅通过 MISO 接收数据, MOSI 引脚无效 (如仅读传感器数据) ;

- **EEPROM READ (Flash 专用)** : 发送 3 字节命令帧 (8 位命令+16 位地址), 用于读取片外 Flash 数据。

#### 2. 时钟配置

- 时钟公式:  $f_{clk\_out} = \frac{f_{spi\_clk}}{SCKDV}$ , 其中, `f_spi_clk` 为 SPI 参考时钟 (最大 48 MHz) , SCKDV 为分频系数 (由 BAUDR 寄存器配置, 取值为 0~65534 的偶数, 最小 2, 对应最高时钟

24 MHz)。

- **时钟极性 (SCPOL) :**

- 0: 空闲时 SCK 为低电平;

- 1: 空闲时 SCK 为高电平。

- **时钟相位 (SCPH) :**

- 0: 数据在 SCK 第一个边沿 (SCPOL=0 为上升沿, SCPOL=1 为下降沿) 采样;

- 1: 数据在 SCK 第二个边沿 (SCPOL=0 为下降沿, SCPOL=1 为上升沿) 采样。

### 3. 线路模式

- **四线模式:** 使用 MOSI、MISO、SCK、NCS, 支持全双工/半双工;

- **三线模式:** MOSI 与 MISO 复用为 DIO 引脚, 仅支持半双工 (发送时用 TX ONLY, 接收时用 RX ONLY)。

### 4. 中断

| 中断类型   | 触发条件                                    | 清除方式                       |

|--------|-----------------------------------------|----------------------------|

| 发送空中断  | 发送 FIFO 数据量 $\leq$ 阈值 (TXFTLR 配置, 0~15) | 写入数据至 FIFO, 使其数据量 $>$ 阈值   |

| 发送溢出中断 | 发送 FIFO 满时继续写入数据                        | 读取 ICR (中断清除寄存器)<br>写 1 清除 |

| 接收满中断  | 接收 FIFO 数据量 $\geq$ 阈值+1 (RXFTLR 配置)     | 读取 FIFO 数据, 使其数据量 $<$ 阈值   |

| 接收溢出中断 | 接收 FIFO 满时继续接收数据                        | 读取 ICR 写 1 清除              |

| 接收欠流中断 | 接收 FIFO 空时尝试读取数据                        | 读取 ICR 写 1 清除              |

### [6.3.2.4] 寄存器映射（以 SPIM0 为例）

SPIM0 基地址: 0x41003000, 其他有关 SPIM0 寄存器配置, 在此基址加上相应的偏移地址。同样地, SPIM1 基地址: 0x41004000, 其他有关 SPIM1 寄存器配置, 在此基址加上相应的偏移地址。

#### 1. 控制寄存器 0 (CTRLR0)

偏移地址: 0x0

| RO   | RO      | RO         | RW      | RW   | RW     | RW    | RW    | RW   | RW    | RW    |

|------|---------|------------|---------|------|--------|-------|-------|------|-------|-------|

| [24] | [22:21] | [20:16]    | [15:12] | [11] | [10]   | [9:8] | [7]   | [6]  | [5:4] | [3:0] |

| SSTE | SPI_FRF | DFS 3<br>2 | CFS     | SRL  | SLV_OE | TMOD  | SCPOL | SCPH | FRF   | DFS   |

|          |                                                 |

|----------|-------------------------------------------------|

| bit[3:0] | DFS: 数据帧大小<br>此寄存器字段仅当 SSI_MAX_XFER_SIZE=16 时有效 |

|----------|-------------------------------------------------|

|          |                                                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit[5:4] | FRF: 帧格式选择。<br>0x0: Motorola SPI 协议<br>0x1: TI SSP 协议<br>0x2: National Microwire 协议<br>0x3: 保留值                                                  |

| bit[6]   | SCPH: 串行时钟相位 Motorola SPI 模式下定义时钟与从机选择信号的时序关系<br>0x0: SCPH_MIDDLE 数据在首个时钟边沿采样 (时钟在首数据位中间翻转)<br>0x1: SCPH_START 数据在第二个时钟边沿采样 (时钟在从机选择激活后延迟一个周期翻转) |

| bit[7]   | SCPOL: 串行时钟极性<br>Motorola SPI 模式下定义空闲时钟电平。 0x0: SCLK_LOW 空闲状态为低电平<br>0x1: SCLK_HIGH 空闲状态为高电平                                                     |

|            |                                                                                                                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit[9:8]   | TMOD: 传输模式。定义数据有效方向<br>0x0: TX_AND_RX 全双工 (TX/RX 均有效)<br>0x1: TX_ONLY 仅发送 (忽略 RX 数据)<br>0x2: RX_ONLY 仅接收 (忽略 TX 数据)<br>0x3: EEPROM_READ EEPROM 读模式 (主机发送控制字后切换为接收, 仅主模式有效)                         |

| bit[10]    | SLV_OE: 从机输出使能仅对从机模式有效<br>0x0: 允许从机正常输出数据 (默认状态)<br>0x1: 强制 ssi_oe_n 为高阻态, 禁用 TXD 输出 (广播模式下防止总线冲突)                                                                                                 |

| bit[11]    | SRL: 移位寄存器环回测试<br>测试专用。将 TX 移位寄存器输出直连至 RX 移位寄存器输入<br>0x0: NORMAL_MODE 正常操作模式<br>0x1: TEST_MODE 环回测试模式 (需外部提供 ss_in_n 和 ssi_clk 信号)                                                                 |

| bit[15:12] | CFS: 控制帧长度 (Microwire 模式)<br>选择 Microwire 帧格式下控制字的位宽                                                                                                                                               |

| bit[20:16] | DFS_32:32 位传输模式下数据帧长度<br>仅当 SSI_MAX_XFER_SIZE=32 时有效。接收数据自动右对齐, 高位补零至 32 位                                                                                                                         |

| bit[22:21] | SPI_FRF: SPI 帧格式选择<br>仅当 SSI_SPI_MODE 配置为 Dual、Quad 或 Octal 模式时<br>有效 0x0: STD_SPI_FRF 标准 SPI 帧格式<br>0x1: Dual_SPI_FRF 双线 SPI 帧格式<br>0x2: Quad_SPI_FRF 四线 SPI 帧格式<br>0x3: Octal_SPI_FRF 八线 SPI 帧格式 |

## 2. 控制寄存器 1 (CTRLR1)

偏移地址: 0x4

| NDF | [15:0] | RW |

|-----|--------|----|

|-----|--------|----|

数据帧数量, 当 TMOD=2 或 TMOD=3 时, 此寄存器字段设置 spi 连续接收的数据帧数。spi 继续接收串行数据, 直到接收到的数据帧数等于此寄存器值加 1, 这使您能够在 连续传输中接收高达 64KB 的数据。当选用 RX ONLY 和 EEPROM READ 模式时 SPI Master 接收数据的个数由寄存器 CTRL1 控制。

## 3. SSI 使能寄存器 (SSIENR)

偏移地址: 0x8

| RW         | RW     |

|------------|--------|

| MODE_3WIRE | SSI_EN |

| [1]        | [0]    |

|      |                                                                                                                                                                          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit0 | SPI使能:<br>启用和禁用所有spi操作。禁用后，所有串行传输将立即停止。当设备被禁用时，发送和接收 FIFO缓冲区被清除。启用时，无法对某些spi控制寄存器进行编程。禁用时，设置ssi_sleep输出（延迟后），通知系统可以安全地删除ssi_clk，从而节省系统的功耗。<br>0x0: 禁用串行传输<br>0x1: 启用串行传输 |

| bit1 | MODE_3WIRE: SPIM3线选择。<br>0x0: 四线模式<br>0x1: 三线模式                                                                                                                          |

#### 4. 从机选择使能寄存器 (SER)

偏移地址: 0x10

| SER | [0] | RW |

|-----|-----|----|

|-----|-----|----|

从机选择使能标志。该寄存器中的每个位对应于来自 spi 主机的从属选择线 (ss\_x\_n)。当该寄存器设置为 1 时，在串行传输开始时，来自主设备的相应从属选择线被激活。在开始传输之前，此寄存器中的设置或清除位对相应的从属选择输出没有影响。在开始传输之前，应该启用此寄存器中与从属设备对应的位。主机想要与之通信的设备。当不在广播模式下操作时，此字段中只应设置一个位。

0x0 (NOT\_SELECTED) : 未选择从属设备; 0x1 (已选择) : 已选择从属设备。

#### 5. 波特率 (时钟分频) 寄存器 (BAUDR)

偏移地址: 0x14

| SCKDV | [15:0] | RW |

|-------|--------|----|

|-------|--------|----|

SSI 时钟分频器。

此字段的 LSB 始终设置为 0，不受写入操作的影响，这确保了此寄存器中保持偶数值。如果该值为 0，则禁用串行输出时钟 (sclk\_out)。sclk\_out 的频率由以下方程式得出：

$$F_{sclkout} = F_{ssiclk}/SCKDV$$

其中 SCKDV 是 2 到 65534 之间的任何偶数值。

#### 6. 发送 FIFO 阈值寄存器 (TXFTLR)

---

偏移地址: 0x18

|        |       |    |

|--------|-------|----|

| TXFTLR | [7:0] | RW |

|--------|-------|----|

发送 FIFO 阈值。

控制传输 FIFO 控制器触发中断的条目级别（或以下）。FIFO 深度可在 2-256 范围内配置；该寄存器的大小被设定为访问 FIFO 所需的地址位数。如果您试图将此值设置为大于或等于 FIFO 的深度，则不会写入此字段并保留其当前值。当传输 FIFO 条目数小于或等于此值时，会触发传输 FIFO 空中断。

## 7. 接收 FIFO 阈值寄存器 (RXFTLR)

偏移地址: 0x1c

|        |       |    |

|--------|-------|----|

| RXFTLR | [7:0] | RW |

|--------|-------|----|

接收 FIFO 阈值。

控制接收 FIFO 控制器触发中断的条目级别（或以上）。FIFO 深度可在 2-256 的范围内配置。该寄存器的大小与访问 FIFO 所需的地址位数相匹配。如果试图将此值设置为大于 FIFO 的深度，则不会写入此字段并保留其当前值。当接收 FIFO 条目数大于或等于 该值+1 时，触发接收 FIFO 满中断。

## 8. 发送 FIFO 当前条目数量寄存器 (TXFLR)

偏移地址: 0x20

|       |        |    |

|-------|--------|----|

| TXFLR | [15:0] | RO |

|-------|--------|----|

发送 FIFO 深度，实时反映发送 FIFO 中有效数据条目数量，范围：0 至 FIFO 深度。

## 9. 接收 FIFO 当前条目数量寄存器 (RXFLR)

偏移地址: 0x24

|       |        |    |

|-------|--------|----|

| RXFLR | [15:0] | RO |

|-------|--------|----|

接收 FIFO 深度,实时反映接收 FIFO 中有效数据条目数量，范围：0 至 FIFO 深度。

## 10. 状态寄存器 (SR)

---

偏移地址: 0x28

| RO   | RO  | RO  | RO   | RO  | RO   | RO   |

|------|-----|-----|------|-----|------|------|

| [6]  | [5] | [4] | [3]  | [2] | [1]  | [0]  |

| DCOL | TXE | RFF | RFNE | TFE | TFNF | BUSY |

|      |                                                                                                |

|------|------------------------------------------------------------------------------------------------|

| bit0 | BUSY: SPI 忙标志<br>置 1 表示当前正在进行串行传输；<br>清 0 表示 SPI 处于空闲或被禁用。                                     |

| bit1 | TFNF:发送 FIFO 未满标志<br>只要发送 FIFO 还有至少一个空位即置 1； FIFO 满时清 0。                                       |

| bit2 | TFE: 发送 FIFO 空标志<br>发送 FIFO 完全空时置 1；只要存在有效条目即清 0。该位不会产生中断请求。                                   |

| bit3 | RFNE: 接收 FIFO 非空标志<br>只要接收 FIFO 中至少有一个有效条目即置 1； FIFO 为空时清 0。软件可轮询此位以确认是否已读空 FIFO。              |

| bit4 | RFF:接收 FIFO 满标志<br>接收 FIFO 完全满时置 1；一旦出现空位即清 0。                                                 |

| bit5 | TXE:发送错误<br>仅从机模式有效，当传输开始时发送 FIFO 为空，则置 1；此时 txd 线会重复上一次的数据。读寄存器后自动清 0。                        |

| bit6 | DCOL: 数据冲突错误<br>仅主机模式有效。当 DW_apb_ssi 作为主机正在传输时，若 ss_in_n 被其它主机拉低，则置1，表示上一次传输被中断未完成。读寄存器后自动清 0。 |

## 11. 中断屏蔽寄存器 (IMR)

偏移地址: 0x2c

| RW    | RW    | RW    | RW    | RW    | RW    |

|-------|-------|-------|-------|-------|-------|

| [5]   | [4]   | [3]   | [2]   | [1]   | [0]   |

| MSTIM | RXFIM | RXOIM | RXUIM | TXOIM | TXEIM |

|      |                                                                |

|------|----------------------------------------------------------------|

| bit0 | TXEIM: 发送FIFO空中断屏蔽<br>0x0: 屏蔽, ssi_txe_intr中断被屏蔽<br>0x1: 开启此中断 |

|------|----------------------------------------------------------------|

|      |                                                                                      |

|------|--------------------------------------------------------------------------------------|

| bit1 | TXOIM:发送FIFO溢出中断屏蔽<br>0x0: 屏蔽, ssi_txo_intr中断被屏蔽<br>0x1: 开启此中断                       |

| bit2 | RXUIM: 接收FIFO 下溢中断屏蔽<br>0x0: 屏蔽, ssi_rxu_intr中断被屏蔽<br>0x1: 开启此中断                     |

| bit3 | RXOIM: 接收 FIFO 溢出中断屏蔽<br>0x0: 屏蔽, ssi_rxo_intr中断被屏蔽<br>0x1: 开启此中断                    |

| bit4 | RXFIM:接收 FIFO 满中断屏蔽<br>0x0: 屏蔽, ssi_rxf_intr中断被屏蔽<br>0x1: 开启此中断                      |

| bit5 | MSTIM:多主机竞争中断屏蔽.<br>如果SPI配置为从机模式，则该位不存在。<br>0x0: 屏蔽, ssi_mst_intr中断被屏蔽<br>0x1: 开启此中断 |

## 12. 中断屏蔽寄存器 (IMR)

偏移地址: 0x30

| RO    | RO    | RO    | RO    | RO    | RO    |

|-------|-------|-------|-------|-------|-------|

| [5]   | [4]   | [3]   | [2]   | [1]   | [0]   |

| MSTIS | RXFIS | RXOIS | RXUIS | TXOIS | TXEIS |

|      |                                                                   |

|------|-------------------------------------------------------------------|

| bit0 | TXEIM: 发送FIFO空中断屏蔽<br>0x0: 屏蔽, ssi_txe_intr中断被屏蔽<br>0x1: 开启此中断    |

| bit1 | TXOIM:发送FIFO溢出中断屏蔽<br>0x0: 屏蔽, ssi_txo_intr中断被屏蔽<br>0x1: 开启此中断    |

| bit2 | RXUIM: 接收FIFO 下溢中断屏蔽<br>0x0: 屏蔽, ssi_rxu_intr中断被屏蔽<br>0x1: 开启此中断  |

| bit3 | RXOIM: 接收 FIFO 溢出中断屏蔽<br>0x0: 屏蔽, ssi_rxo_intr中断被屏蔽<br>0x1: 开启此中断 |

|      |                                                                                      |

|------|--------------------------------------------------------------------------------------|

| bit4 | RXFIM:接收 FIFO 满中断屏蔽<br>0x0: 屏蔽, ssi_rxf_intr中断被屏蔽<br>0x1: 开启此中断                      |

| bit5 | MSTIM:多主机竞争中断屏蔽。<br>如果SPI配置为从机模式，则该位不存在。<br>0x0: 屏蔽, ssi_mst_intr中断被屏蔽<br>0x1: 开启此中断 |

### 13. 中断状态寄存器 (ISR)

偏移地址: 0x30

| RO    | RO    | RO    | RO    | RO    | RO    |

|-------|-------|-------|-------|-------|-------|

| [5]   | [4]   | [3]   | [2]   | [1]   | [0]   |

| MSTIS | RXFIS | RXOIS | RXUIS | TXOIS | TXEIS |

|      |                                                                                                         |

|------|---------------------------------------------------------------------------------------------------------|

| bit0 | TXEIS:发送FIFO空中断状态位<br>0x0: 无效, ssi_txe_intr中断无效（未触发）<br>0x1: 有效, ssi_txe_intr中断有效（触发）                   |

| bit1 | TXOIS:发送FIFO溢出中断状态位<br>0x0: 无效, ssi_txo_intr中断无效（未触发）<br>0x1: 有效, ssi_txo_intr中断有效（触发）                  |

| bit2 | RXUIS: 接收FIFO 下溢中断状态位<br>0x0: 无效, ssi_rxu_intr中断无效（未触发）<br>0x1: 有效, ssi_rxu_intr中断有效（触发）                |

| bit3 | RXOIS: 接收 FIFO 溢出中断状态位<br>0x0: 无效, ssi_rxo_intr中断无效（未触发）<br>0x1: 有效, ssi_rxo_intr中断有效（触发）               |

| bit4 | RXFIS:接收 FIFO 满中断状态位<br>0x0: 无效, ssi_rxf_intr中断无效（未触发）<br>0x1: 有效, ssi_rxf_intr中断有效（触发）                 |

| bit5 | MSTIS:多主机竞争中断状态位如果SPI配置为从机模式，则该位不存在。<br>0x0: 无效, ssi_mst_intr中断无效（未触发）<br>0x1: 有效, ssi_mst_intr中断有效（触发） |

### 14. 中断清除寄存器 (ICR)

偏移地址: 0x48

|     |     |    |

|-----|-----|----|

| ICR | [0] | RO |

|-----|-----|----|

清除中断。

如果下面的任何中断有效，则该寄存器置位。读操作会清除 ssi\_txo\_intr、ssi\_rxu\_intr、ssi\_rxo\_intr 和 ssi\_mst\_intr 中断。

## 15.数据寄存器 (DR16)

偏移地址：0x60

|      |        |    |

|------|--------|----|

| DR16 | [15:0] | RW |

|------|--------|----|

数据寄存器。

写入该寄存器时，数据自动右对齐。如果 SSI\_MAX\_XFER\_SIZE 配置参数设置为 32，则所有 32 位都有效。否则，寄存器中只有 16 位([15:0])有效。

### 6.3.3 SPI Slave

#### [6.3.3.1] 简介

SPI Slave 被动响应 SPI Master 的通信请求，时钟 (SCK) 由 Master 提供，仅在 NCS (片选) 有效时与 Master 交互数据。BL1820 的 SPI Slave 支持四线、三线、两线模式，适用于作为从设备接收主机控制指令（如传感器数据上传、配置接收）。

#### [6.3.3.2] 主要特性

| 特性分类 | 具体参数/功能                                         |

|------|-------------------------------------------------|

| 通信模式 | 全双工四线、半双工四线、半双工三线、半双工两线（无 NCS，片选由寄存器控制）         |

| 帧格式  | 8-bit/16-bit 可选                                 |

| 时钟性能 | 最高支持 ( $f_{PCLK}/4$ ) (PCLK 为外设时钟，最大 48 MHz，对应最 |

| 特性分类    | 具体参数/功能                                      |

|---------|----------------------------------------------|

|         | 高 12 MHz)                                    |

| FIFO 缓冲 | 发送/接收 FIFO 深度均为 16 字节，支持 FIFO 阈值中断           |

| 线路灵活性   | 两线模式下 MOSI/MISO 复用为 DIO，NCS 由内部寄存器控制（无需外部引脚） |

| 中断支持    | 与 SPI Master 一致（发送空、发送溢出、接收满、接收溢出、接收欠流）      |

### [6.3.3.3] 功能描述

#### 1. 传输模式

通过 `CTRLR0` 寄存器配置，支持 3 种传输模式：

- **TX AND RX (全双工)**：接收 Master 数据的同时，向 Master 发送反馈数据；

- **TX ONLY (半双工发送)**：仅向 Master 发送数据，不接收（如传感器主动上传数据）；

- **RX ONLY (半双工接收)**：仅接收 Master 数据，不发送（如接收主机配置指令）。

#### 2. 时钟特性

- **时钟来源**：完全由 SPI Master 提供，Slave 无需配置时钟分频，仅需确保 `SCPOL/SCPH` 与 Master 一致；

- **采样时序**：与 SPI Master 相同（`SCPH=0` 在第一个边沿采样，`SCPH=1` 在第二个边沿采样），需提前与 Master 协商配置。

#### 3. 线路模式

- **四线模式**: MOSI (收)、MISO (发)、SCK (时钟)、NCS (片选)，全双工/半双工；

- **三线模式**: MOSI 与 MISO 复用为 DIO 引脚，半双工 (发送时用 TX ONLY, 接收时用 RX ONLY)；

- **两线模式**: 仅使用 SCK 和 DIO, NCS 由 SPIS\_NCS\_CTRL 寄存器控制 (1=选中, 0=未选中)，适用于引脚资源紧张的场景。

## 4. 中断

与 SPI Master 中断类型完全一致，仅触发条件依赖 Master 的通信节奏（如 Master 发送数据时 Slave 接收 FIFO 满触发中断），清除方式相同（读取 ICR 寄存器写 1）。

### [6.3.3.4] 寄存器映射 (SPIS)

SPI Slave 基址: 0x41007000, 其他有关 SPIS 寄存器配置，在此基址加上相应的偏移地址。

#### 1. 控制寄存器 0 (CTRLR0)

偏移地址: 0x0

|      |         |         |         |      |        |       |       |      |       |       |

|------|---------|---------|---------|------|--------|-------|-------|------|-------|-------|

| RO   | RO      | RO      | RW      | RW   | RW     | RW    | RW    | RW   | RW    | RW    |

| [24] | [22:21] | [20:16] | [15:12] | [11] | [10]   | [9:8] | [7]   | [6]  | [5:4] | [3:0] |

| SSTE | SPI_FRF | DFS_32  | CFS     | SRL  | SLV_OE | TMOD  | SCPOL | SCPH | FRF   | DFS   |

|          |                                                                                         |

|----------|-----------------------------------------------------------------------------------------|

| bit[3:0] | DFS: 数据帧大小<br>此寄存器字段仅当 SSI_MAX_XFER_SIZE=16 时有效                                         |

| bit[5:4] | FRF: 帧格式选择。 0x0: Motorola SPI协议<br>0x1: TI SSP协议<br>0x2:National Microwire协议<br>0x3:保留值 |

|          |                                                                                                                                                                 |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit[6]   | SCPH: 串行时钟相位Motorola SPI模式下定义时钟与从机选择信号的时序关系<br>0x0: SCPH_MIDDLE 数据在首个时钟边沿采样（时钟在首数据位中间翻转）<br>0x1: SCPH_START 数据在第二个时钟边沿采样（时钟在从机选择激活后延迟一个周期翻转）                    |

| bit[7]   | SCPOL: 串行时钟极性<br>Motorola SPI模式下定义空闲时钟电平。<br>0x0: SCLK_LOW 空闲状态为低电平<br>0x1: SCLK_HIGH 空闲状态为高电平                                                                  |

| bit[9:8] | TMOD: 传输模式。定义数据有效方向<br>0x0: TX_AND_RX 全双工（TX/RX均有效）<br>0x1: TX_ONLY 仅发送（忽略RX数据）<br>0x2: RX_ONLY 仅接收（忽略TX数据）<br>0x3: EEPROM_READ EEPROM读模式（主机发送控制字后切换为接收，仅主模式有效） |

| bit[10]  | SLV_OE: 从机输出使能仅对从机模式有效<br>0x0: 允许从机正常输出数据（默认状态）<br>0x1: 强制ssi_oe_n为高阻态，禁用TXD输出（广播模式下防止总线冲突）                                                                     |

| bit[11]  | SRL: 移位寄存器环回测试<br>测试专用。将TX移位寄存器输出直连至RX移位寄存器输入<br>0x0: NORMAL_MODE 正常操作模式<br>0x1: TEST_MODE 环回测试模式（需外部提供ss_in_n和ssi_clk信号）                                       |

|            |                                                                                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit[15:12] | CFS: 控制帧长度 (Microwire模式)<br>选择Microwire帧格式下控制字的位宽                                                                                                                                     |

| bit[20:16] | DFS_32:32位传输模式下数据帧长度<br>仅当SSI_MAX_XFER_SIZE=32时有效。接收数据自动右对齐，高位补零至32位                                                                                                                  |

| bit[22:21] | SPI_FRF:SPI帧格式选择<br>仅当SSI_SPI_MODE配置为Dual、Quad或Octal模式时有效<br>0x0 : STD_SPI_FRF 标准SPI帧格式<br>0x1 : Dual_SPI_FRF 双线SPI帧格式<br>0x2 : Quad_SPI_FRF 四线SPI帧格式<br>0x3 : Octal_SPI_FRF 八线SPI帧格式 |

| bit[24]    | SSTE:从机选择信号反转使能<br>在SPI模式下，当时钟相位 (SCPH) 设为0时，该寄存器控制数据帧间从机选择信号线 (ss_*n) 的行为                                                                                                            |

## 2. SSI 使能寄存器 (SSIENR)

偏移地址: 0x8

| RW       | RW       | RW      | RW         | RW     |

|----------|----------|---------|------------|--------|

| NCS_MODE | FRX_MODE | FIFO_EN | MODE_3WIRE | SSI_EN |

| [5:4]    | [3]      | [2]     | [1]        | [0]    |

|      |                                                                                                                                                                          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit0 | SPI使能:<br>启用和禁用所有spi操作。禁用后，所有串行传输将立即停止。当设备被禁用时，发送和接收FIFO缓冲区被清除。启用时，无法对某些spi控制寄存器进行编程。禁用时，设置 ssi_sleep输出（延迟后），通知系统可以安全地删除ssi_clk，从而节省系统的功耗。<br>0x0: 禁用串行传输<br>0x1: 启用串行传输 |

| bit1 | MODE_3WIRE: SPIM3线选择。<br>0x0: 四线模式<br>0x1: 三线模式                                                                                                                          |

| bit2 | FIFO强制使能:<br>0x0: 当SSI_EN为0， FIFO失能<br>0x1: 当SSI_EN为1， FIFO使能                                                                                                            |

| bit3 | FIFO接收模式控制:<br>0x0:正常模式<br>0x1:CPHA=1， 快速写入数据以满足3线定时                                                                                                                     |

|          |                                                                       |

|----------|-----------------------------------------------------------------------|

| bit[5:4] | NCS处理模式:<br>0x0: 正常进行<br>0x1: 过滤一个高脉冲<br>0x2: 过滤两个高脉冲<br>0x3: 过滤一个低脉冲 |

|----------|-----------------------------------------------------------------------|

### 3. 发送 FIFO 阈值寄存器 (TXFTLR)

偏移地址: 0x18

|        |       |    |

|--------|-------|----|

| TXFTLR | [7:0] | RW |

|--------|-------|----|

发送 FIFO 阈值。

控制传输 FIFO 控制器触发中断的条目级别（或以下）。FIFO 深度可在 2-256 范围内 配置；该寄存器的大小被设定为访问 FIFO 所需的地址位数。如果您试图将此值设置为 大于或等于 FIFO 的深度，则不会写入此字段并保留其当前值。当传输 FIFO 条目数小于 或等于此值时，会触发传输 FIFO 空中断。

### 4. 接收 FIFO 阈值寄存器 (RXFTLR)

偏移地址: 0x1c

|        |       |    |

|--------|-------|----|

| RXFTLR | [7:0] | RW |

|--------|-------|----|

接收 FIFO 阈值。

控制接收 FIFO 控制器触发中断的条目级别（或以上）。FIFO 深度可在 2-256 的范围 内配置。该寄存器的大小与访问 FIFO 所需的地址位数相匹配。如果试图将此值设置为 大于 FIFO 的深度，则不会写入此字段并保留其当前值。当接收 FIFO 条目数大于或等于 该值+1 时，触发接收 FIFO 满中断。

### 5. 发送 FIFO 当前条目数量寄存器 (TXFLR)

偏移地址: 0x20

|       |        |    |

|-------|--------|----|

| TXFLR | [15:0] | RO |

|-------|--------|----|

发送 FIFO 深度，实时反映发送 FIFO 中有效数据条目数量，范围：0 至 FIFO 深度。

### 6. 接收 FIFO 当前条目数量寄存器 (RXFLR)

偏移地址: 0x24

|       |        |    |

|-------|--------|----|

| RXFLR | [15:0] | RO |

|-------|--------|----|

接收 FIFO 深度, 实时反映接收 FIFO 中有效数据条目数量, 范围: 0 至 FIFO 深度。

## 7. 状态寄存器 (SR)

偏移地址: 0x28

|      |     |     |      |     |      |      |

|------|-----|-----|------|-----|------|------|

| RO   | RO  | RO  | RO   | RO  | RO   | RO   |

| [6]  | [5] | [4] | [3]  | [2] | [1]  | [0]  |

| DCOL | TXE | RFF | RFNE | TFE | TFNF | BUSY |

|      |                                                                                                    |

|------|----------------------------------------------------------------------------------------------------|

| bit0 | BUSY: SPI 忙标志<br>置 1 表示当前正在进行串行传输; 清 0 表示 SPI 处于空闲或被禁用。                                            |

| bit1 | TFNF: 发送 FIFO 未满标志<br>只要发送 FIFO 还有至少一个空位即置 1; FIFO 满时清 0。                                          |

| bit2 | TFE: 发送 FIFO 空标志<br>发送 FIFO 完全空时置 1; 只要存在有效条目即清 0。该位不会产生中断请求。                                      |

| bit3 | RFNE: 接收 FIFO 非空标志<br>只要接收 FIFO 中至少有一个有效条目即置 1; FIFO 为空时清 0。软件可轮询此位以确认是否已读空 FIFO。                  |

| bit4 | RFF: 接收 FIFO 满标志<br>接收 FIFO 完全满时置 1; 一旦出现空位即清 0。                                                   |

| bit5 | TXE: 发送错误<br>仅从机模式有效, 当传输开始时发送 FIFO 为空, 则置 1; 此时 txd 线会重复上一次的数据。读寄存器后自动清 0。                        |

| bit6 | DCOL: 数据冲突错误<br>仅主机模式有效。当 DW_apb_ssi 作为主机正在传输时, 若 ss_in_n 被其它主机拉低, 则置 1, 表示上一次传输被中断未完成。读寄存器后自动清 0。 |

## 8. 中断屏蔽寄存器 (IMR)

偏移地址: 0x2c

|    |    |    |    |    |

|----|----|----|----|----|

| RW | RW | RW | RW | RW |

|----|----|----|----|----|

| [4]   | [3]   | [2]   | [1]   | [0]   |

|-------|-------|-------|-------|-------|

| RXFIM | RXOIM | RXUIM | TXOIM | TXEIM |

|      |                                                                   |

|------|-------------------------------------------------------------------|

| bit0 | TXEIM: 发送FIFO空中断屏蔽<br>0x0: 屏蔽, ssi_txe_intr中断被屏蔽<br>0x1: 开启此中断    |

| bit1 | TXOIM:发送FIFO溢出中断屏蔽<br>0x0: 屏蔽, ssi_txo_intr中断被屏蔽<br>0x1: 开启此中断    |

| bit2 | RXUIM: 接收FIFO 下溢中断屏蔽<br>0x0: 屏蔽, ssi_rxu_intr中断被屏蔽<br>0x1: 开启此中断  |

| bit3 | RXOIM: 接收 FIFO 溢出中断屏蔽<br>0x0: 屏蔽, ssi_rxo_intr中断被屏蔽<br>0x1: 开启此中断 |

| bit4 | RXFIM:接收 FIFO 满中断屏蔽<br>0x0: 屏蔽, ssi_rxf_intr中断被屏蔽<br>0x1: 开启此中断   |

## 9. 中断状态寄存器 (ISR)

偏移地址: 0x30

| RO    | RO    | RO    | RO    | RO    |

|-------|-------|-------|-------|-------|

| [4]   | [3]   | [2]   | [1]   | [0]   |

| RXFIS | RXOIS | RXUIS | TXOIS | TXEIS |

|      |                                                                                            |

|------|--------------------------------------------------------------------------------------------|

| bit0 | TXEIS: 发送FIFO空中断状态位<br>0x0: 无效, ssi_txe_intr中断无效 (未触发)<br>0x1: 有效, ssi_txe_intr中断有效 (触发)   |

| bit1 | TXOIS:发送FIFO溢出中断状态位<br>0x0: 无效, ssi_txo_intr中断无效 (未触发)<br>0x1: 有效, ssi_txo_intr中断有效 (触发)   |

| bit2 | RXUIS: 接收FIFO 下溢中断状态位<br>0x0: 无效, ssi_rxu_intr中断无效 (未触发)<br>0x1: 有效, ssi_rxu_intr中断有效 (触发) |

|      |                                                                                           |

|------|-------------------------------------------------------------------------------------------|

| bit3 | RXOIS: 接收 FIFO 溢出中断状态位<br>0x0: 无效, ssi_rxo_intr中断无效（未触发）<br>0x1: 有效, ssi_rxo_intr中断有效（触发） |

| bit4 | RXFIS:接收 FIFO 满中断状态位<br>0x0: 无效, ssi_rxf_intr中断无效（未触发）<br>0x1: 有效, ssi_rxf_intr中断有效（触发）   |

## 10. 中断清除寄存器 (ICR)

偏移地址: 0x48

|     |     |    |

|-----|-----|----|

| ICR | [0] | RO |

|-----|-----|----|

清除中断。

如果下面的任何中断有效，则该寄存器置位。读操作会清除 ssi\_txo\_intr 、 ssi\_rxu\_intr、 ssi\_rxo\_intr 和 ssi\_mst\_intr 中断。

## 11. 数据寄存器 (DR16)

偏移地址: 0x60

|      |        |    |

|------|--------|----|

| DR16 | [15:0] | RW |

|------|--------|----|

数据寄存器。

写入该寄存器时，数据自动右对齐。如果 SSI\_MAX\_XFER\_SIZE 配置参数设置为 3 2，则所有 32 位都有效。否则，寄存器中只有 16 位([15:0])有效。

## 6.4 GPIO

### 6.4.1 简介

BL1820 内部包含 24 个通用输入/输出口 (GPIO0~GPIO23) , 支持数字输入/输出、模拟输入、外设复用，可配置上拉/下拉、开漏/推挽输出、中断触发方式。

### 6.4.2 主要特性

- 输入模式：浮空、上拉、下拉、模拟输入；

- 输出模式：推挽（4 档驱动能力）、开漏；

- 中断：支持高电平、低电平、上升沿、下降沿、任意边沿触发；

- 唤醒：所有 GPIO 可配置为深度休眠模式唤醒源；

- 复用：支持 UART、SPI、IIC、Timer 等外设复用。

### 6.4.3 功能描述

#### [6.4.3.1] 输入配置

- **浮空输入**: 无上下拉电阻，适用于外部有电平驱动的场景；

- **上拉输入**: 内部上拉电阻（25 kΩ 典型值），默认电平为高；

- **下拉输入**: 内部下拉电阻（25 kΩ 典型值），默认电平为低；

- **模拟输入**: 禁用数字电路，用于 ADC 采样。

#### [6.4.3.2] 输出配置

- **推挽输出**: 可输出高/低电平，驱动能力分 4 档（通过 GPIO\_CFG\_N[4:3] 配置，11>10>01>00）；

- **开漏输出**: 仅能拉低电平，高电平需外部上拉电阻，适用于 IIC 总线等多设备共享总线场景。

#### [6.4.3.3] 中断配置

每个 GPIO 的中断通过以下寄存器配置：

- **GPIO\_IT\_HI**: 高电平中断使能；

- **GPIO\_IT\_LO**: 低电平中断使能；

- **GPIO\_IT\_PEDGE**: 上升沿中断使能；

- **GPIO\_IT\_NEDGE**: 下降沿中断使能；

- **GPIO\_INT\_STATUS**: 中断状态寄存器（读 1 表示对应 GPIO 触发中断）；

### 6.4.4 寄存器映射

GPIO 基地址: 0x40010000，其他 GPIO 功能配置寄存器地址加上相应的偏移地址。

#### 1. 输入电平状态 (GPIO\_I)

偏移地址: 0x20

使用 GPIO 用作数字端口时，通过 GPIO\_I[23:0] 寄存器查看端口输入情况。

对应 bit 为 1 时表示端口输入电平为高电平，为 0 时表示端口输入电平为低电平。

| RO         |

|------------|------------|------------|------------|------------|------------|------------|------------|

| GPIO_I[23] | GPIO_I[22] | GPIO_I[21] | GPIO_I[20] | GPIO_I[19] | GPIO_I[18] | GPIO_I[17] | GPIO_I[16] |

| RO         |

|            |            |            |            |            |            |           |           |

|------------|------------|------------|------------|------------|------------|-----------|-----------|

| GPIO_I[15] | GPIO_I[14] | GPIO_I[13] | GPIO_I[12] | GPIO_I[11] | GPIO_I[10] | GPIO_I[9] | GPIO_I[8] |

| RO         | RO         | RO         | RO         | RO         | RO         | RO        | RO        |

| GPIO_I[7]  | GPIO_I[6]  | GPIO_I[5]  | GPIO_I[4]  | GPIO_I[3]  | GPIO_I[2]  | GPIO_I[1] | GPIO_I[0] |

对于不同的 GPIO\_I[x]取值，0: 低电平；1: 高电平，所有引脚均为只读。

## 2. IO 输入/输出方向选择 (GPIO\_OE)

偏移地址: 0x30

使用 GPIO 用作数字端口时，通过 GPIO\_OE[23:0]寄存器控制方向。对应 bit 为 1 时端口 方向为输出，为 0 时端口方向为输入。

|             |             |             |             |             |             |             |             |

|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| RW          |

| GPIO_OE[23] | GPIO_OE[22] | GPIO_OE[21] | GPIO_OE[20] | GPIO_OE[19] | GPIO_OE[18] | GPIO_OE[17] | GPIO_OE[16] |

| RW          |

| GPIO_OE[15] | GPIO_OE[14] | GPIO_OE[13] | GPIO_OE[12] | GPIO_OE[11] | GPIO_OE[10] | GPIO_OE[9]  | GPIO_OE[8]  |

| RW          |

| GPIO_OE[7]  | GPIO_OE[6]  | GPIO_OE[5]  | GPIO_OE[4]  | GPIO_OE[3]  | GPIO_OE[2]  | GPIO_OE[1]  | GPIO_OE[0]  |

对于不同的 GPIO\_OE[x]取值为： 0: 使能输出；1: 失能输出

## 3. 输出高低电平选择 (GPIO\_O)

偏移地址: 0x40

使用 GPIO 用作数字端口时，通过 GPIO\_O[23:0]寄存器控制端口输出电平。

对应 bit 为 1 时端口输出电平为高电平，为 0 时端口输出电平为低电平。

|            |            |            |            |            |            |            |            |

|------------|------------|------------|------------|------------|------------|------------|------------|

| RW         |

| GPIO_O[23] | GPIO_O[22] | GPIO_O[21] | GPIO_O[20] | GPIO_O[19] | GPIO_O[18] | GPIO_O[17] | GPIO_O[16] |

| RW         |

| GPIO_O[15] | GPIO_O[14] | GPIO_O[13] | GPIO_O[12] | GPIO_O[11] | GPIO_O[10] | GPIO_O[9]  | GPIO_O[8]  |

| RW         |

| GPIO_O[7]  | GPIO_O[6]  | GPIO_O[5]  | GPIO_O[4]  | GPIO_O[3]  | GPIO_O[2]  | GPIO_O[1]  | GPIO_O[0]  |

当 GPIO 功能为正常 GPIO，GPIO\_oe 为“1”时，生效。对于不同的 GPIO\_O[x]取值为： 0:低电平；1: 高电平

## 4. 端口配置寄存器 (GPIO\_CFG\_N)

偏移地址: 0x200

GPIO 寄存器划分为 6 组，即 GPIO\_CFG\_[0..5]。每个 GPIO\_CFG\_N[32:0]寄存器包含有 4 个 GPIO 端口的配置信息，每个端口信息占 8 个 bit。

| [31:24]   | [23:16]   | [15:8]    | [7:0]     |

|-----------|-----------|-----------|-----------|

| gpio3_cfg | gpio2_cfg | gpio1_cfg | gpio0_cfg |

对于每个 gpio\_cfg\_0 组中的单个 GPIO 端口来说，8 个 bit 的配置如下：

|          |                                                                                      |

|----------|--------------------------------------------------------------------------------------|

| bit[2:0] | GPIO功能选择：具体使用查看端口复用说明（表1）                                                            |

| bit[4:3] | 驱动强度控制：<br>0x0: 3mA<br>0x1: 9mA<br>0x2: 15mA<br>0x3: 21mA                            |

| bit[7:5] | GPIO模式控制：<br>0x0: 输入浮空<br>0x1:上拉输入<br>0x2: 下拉输入<br>0x3: 模拟输入<br>0x4: 开漏模式<br>其他: 高阻抗 |

注：推挽输出模式：需要端口配置为[7:5]000 后，再配置 GPIO 输出使能寄存器 (GPIO\_OE)

## 5. GPIO 使能寄存器(GPIO\_IE)

偏移地址：0x140

|         |        |    |

|---------|--------|----|

| gpio_ie | [23:0] | RW |

|---------|--------|----|

描述：通过设置对应位，使能/失能对应引脚[23:0]中断，0:Disable/1:Enable

## 6. GPIO 清除中断寄存器(GPIO\_IS)

偏移地址：0x150

|         |        |    |

|---------|--------|----|

| gpio_is | [23:0] | RW |

|---------|--------|----|

描述：清除 GPIO 引脚[23:0]的中断状态，写入“1”清除对应位

## 7. GPIO 屏蔽中断寄存器(GPIO\_MIS)

偏移地址：0x160

|          |        |      |

|----------|--------|------|

| gpio_mis | [23:0] | RW1C |

|----------|--------|------|

描述：每个 GPIO 屏蔽中断状态，写入“1”清除相应位

## 8. GPIO 高电平中断寄存器(GPIO\_IT\_HI)

偏移地址: 0x170

|            |        |      |

|------------|--------|------|

| gpio_it_hi | [23:0] | RW1C |

|------------|--------|------|

描述: 启用 GPIO[23:0]引脚高电平中断, 可以与其他中断条件一起设置,

以启用多 条件中断

## 9. GPIO 低电平中断寄存器(GPIO\_IT\_LO)

偏移地址: 0x180

|            |        |    |

|------------|--------|----|

| gpio_it_lo | [23:0] | RW |

|------------|--------|----|

描述: 启用 GPIO[23:0]引脚低电平中断, 可以与其他中断条件一起设置,

以启用多 条件中断

## 10. GPIO 上升沿中断寄存器(GPIO\_IT\_PEDGE)

偏移地址: 0x190

|               |        |     |

|---------------|--------|-----|

| gpio_it_pedge | [23:0] | R/W |

|---------------|--------|-----|

描述: 启用 GPIO[23:0]引脚上升沿中断, 可以与其他中断条件一起设置,

以启用多 条件中断

## 12. GPIO 下降沿中断寄存器(GPIO\_IT\_NEDGE)

偏移地址: 0x1a0

|               |        |     |

|---------------|--------|-----|

| gpio_it_nedge | [23:0] | R/W |

|---------------|--------|-----|

描述: 启用 GPIO[23:0]引脚上升沿中断, 可以与其他中断条件一起设置,

以启用多 条件中断。

## 12. GPIO 重映射控制寄存器 0(GPIO\_REMAP\_CTRL0)

偏移地址: 0x300

| RW             | RW             | RW             | RW             | RW             | RW             |

|----------------|----------------|----------------|----------------|----------------|----------------|

| [22:20]        | [18:16]        | [14:12]        | [10:8]         | [6:4]          | [2:0]          |

| qspi0_pin5_sel | qspi0_pin4_sel | qspi0_pin3_sel | qspi0_pin2_sel | qspi0_pin1_sel | qspi0_pin0_sel |

|            |                                                                                                                                                                                                                                                       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit[2:0]   | qspi0_pin0_sel:QSPI0_NCS 引脚功能重映射选择, 取值与 qspi0_pin5_sel 完全一致, 复位默认 0x0                                                                                                                                                                                 |

| bit[6:4]   | qspi0_pin1_sel:QSPI0_SCK 引脚功能重映射选择, 取值与 qspi0_pin5_sel 完全一致, 复位默认 0x1                                                                                                                                                                                 |

| bit[10:8]  | qspi0_pin2_sel:QSPI0_D0 引脚功能重映射选择, 取值与 qspi0_pin5_sel 完全一致, 复位默认 0x2                                                                                                                                                                                  |

| bit[14:12] | qspi0_pin3_sel:QSPI0_D1 引脚功能重映射选择, 取值与 qspi0_pin5_sel 完全一致, 复位默认 0x3                                                                                                                                                                                  |

| bit[18:16] | qspi0_pin4_sel:QSPI0_D2 引脚功能选择, 取值与 qspi0_pin5_sel 完全一致, 复位默认 0x4                                                                                                                                                                                     |

| bit[22:20] | <p>qspi0_pin5_sel:QSPI0_D3 引脚功能选择<br/>           0x0: 映射为 QSPI_NCS<br/>           0x1: 映射为 QSPI_SCK<br/>           0x2: 映射为 QSPI_D0<br/>           0x3: 映射为 QSPI_D1<br/>           0x4: 映射为 QSPI_D2<br/>           0x5: 映射为 QSPI_D3 (复位默认值, 正常使用)</p> |

### 13. GPIO 重映射控制寄存器 1(GPIO\_REMAP\_CTRL1)

偏移地址: 0x304

| RW             | RW             | RW             | RW             | RW            | RW            |

|----------------|----------------|----------------|----------------|---------------|---------------|

| [31:30]        | [29:28]        | [27:26]        | [25:24]        | [1]           | [0]           |

| spis0_pin3_sel | spis0_pin2_sel | spis0_pin1_sel | spis0_pin0_sel | i2c0_pin1_sel | i2c0_pin0_sel |

|            |                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------|

| bit[0]     | i2c0_pin0_sel:I2C0_SCL 引脚功能重映射选择<br>0x0: 将该引脚配置为 I2C0_SCL 功能 (复位默认值)<br>0x1: 将该引脚配置为 I2C0_SDA 功能  |

| bit[1]     | i2c0_pin1_sel:I2C0_SDA 引脚功能重映射选择器<br>0x0: 将该引脚配置为 I2C0_SCL 功能<br>0x1: 将该引脚配置为 I2C0_SDA 功能 (复位默认值) |

| bit[25:24] | spis0_pin0_sel:SPIS0_NCS 引脚功能重映射选择, 取值与 spis0_pin3_sel 完全一致, 复位默认 0x0                             |

| bit[27:26] | spis0_pin1_sel:SPIS0_SCK 引脚功能重映射选择, 取值与 spis0_pin3_sel 完全一致, 复位默认 0x1                             |

| bit[29:28] | spis0_pin2_sel:SPIS0_MOSI 引脚功能重映射选择, 取值与 spis0_pin3_sel 完全一致, 复位默认 0x2                            |

|            |                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| bit[31:30] | spis0_pin3_sel:SPIS0_MISO 引脚功能重映射选择<br>0x0: 配置为 SPIS0_NCS 功能<br>0x1: 配置为 SPIS0_SCK 功能<br>0x2: 配置为 SPIS0_MOSI 功能<br>0x3: 配置为 SPIS0_MISO 功能 (复位默认值) |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

## 6.5 UART

### 6.5.1 简介

BL1820 包含的 UART 支持异步全双工串行通信，用于与 PC、模块等外设通信，最高波特率 2 Mbps。

### 6.5.2 主要特性

- 波特率：1200 ~ 2 Mbps（可配置，时钟源可选 RC\_24M、XTAL\_24M、DPLL\_48M）；

- 数据格式：8/9 位数据位、1/1.5/2 位停止位、奇偶校验（奇/偶/无）；

- FIFO：发送/接收 FIFO 深度均为 16 字节；

- 错误检测：溢出错误（OE）、帧错误（FE）、奇偶错误（PE）；

- 中断：发送空、接收满、线路错误、BUSY 中断。

### 6.5.3 功能描述

#### [6.5.3.1] 波特率计算

UART 波特率公式：

$$\text{Baudrate} = f_{uartclk}(16 * \text{DIVISOR})$$

- (`f_uart_clk`)：UART 参考时钟（RC\_24M/XTAL\_24M 支持最高 1.5 Mbps，DPLL\_48M 支持最高 2 Mbps）；

- DIVISOR：分频系数（整数部分 DIVN+小数部分 DLF/16，DIVN 由 `DLH`（高 8 位）和 `DLL`（低 8 位）控制，DLF 由 `DLF` 寄存器控制，精度 1/16）。

示例：配置波特率 115200，时钟 48 MHz

1. (`DIVISOR = 48000000 / (16 * 115200) ≈ 26.0417`)；

2. `DIVN=26` (`DLH=0x00`, `DLL=0x1A`)，`DLF=0.0417 * 16 ≈ 1` (`DLF=0x01`)；

3. 实际波特率= $48000000 / (16 * (26 + 1/16)) \approx 114942.5$  bps (误差<0.2%)。

### [6.5.3.2] 硬件自动流控

- **Auto RTS:** 接收 FIFO 数据量达到阈值（1/4/8/14 字节，FCR[7:6]配置）时，RTS 输出高电平，通知发送方暂停发送；FIFO 空时，RTS 输出低电平，允许继续发送；

- **Auto CTS:** CTS 输入高电平时，禁用 UART 发送器；CTS 输入低电平时，恢复发送。

### [6.5.3.3] 中断

UART 支持以下四种中断，可通过配置寄存器 IER 启用：

- **发送空中断:** 当 UART 发送 FIFO 里没有数据时触发该中断。清除方法：读取寄存器 IIR 或者往 FIFO 里写入数据使其电平大于发送阈值。

- **接收满中断:** 当 UART 接收 FIFO 里的数据个数大于阈值时触发该中断。清除方法：当没有启用 FIFO 时读取 RBR 寄存器；当启用 FIFO 时读取 FIFO 使其电平低于阈值。

- **线路错误检测中断:** 当接收线路上的数据存在帧错误、校验错误或者有溢出时将会触发该中断。清除方法：读取寄存器 RBR 或者 LSR。

- **BUSY 中断:** 在 UART 进行通信时设置寄存器 LCR 将会触发该中断。清除方法：读取寄存器 USR。

### 6.5.4 寄存器映射 (UART0)

UART0 基地址: 0x41001000, 其他 UART0 功能配置寄存器地址加上相应的偏移地址。同样地, UART1 基地址: 0x41002000, 其他 UART1 功能配置寄存器地址加上相应的偏移地址。

#### 1. 接收缓冲寄存器(RBR)

偏移地址: 0x0

| RBR | [8:0] | RO |

|-----|-------|----|

|-----|-------|----|

该寄存器包含 UART 模式下串行输入端口 (sin) 或红外模式下串行红外输入 (sir\_in) 接收到的数据字节。仅当线路状态寄存器 (LSR) 中的数据就绪 (DR) 位设置时, 此寄存器中的数据才有效。只有当 DLAB 位 (LCR[7]) 被清除时, 才能访问此寄存器。当 9BIT\_DATA\_EN = 0 时, 字段宽度为 8。9BIT\_DATA\_EN = 1, 字段宽度为 9。

#### 2. 发送保持寄存器(THR)

偏移地址: 0x0

| THR | [8:0] | WO |

|-----|-------|----|

|-----|-------|----|

该寄存器包含在 UART 模式下通过串行输出端口 (sout) 传输的数据, 或在红外模式下通过红外串行输出 (sir\_out\_n) 传输的信息。只有当设置了 THRE 位 (LSR[5]) 时, 才应将数据写入 THR。只有当 DLAB 位 (LCR[7]) 被清除时, 才能访问此寄存器。当 9BIT\_DATA\_EN = 0 时, 字段宽度为 8。9BIT\_DATA\_EN = 1, 字段宽度为 9。

#### 3. 除数锁存寄存器(整数部分低 8 位) (DLL)

偏移地址: 0x0

| DLL | [7:0] | RW |

|-----|-------|----|

|-----|-------|----|

该寄存器构成了一个 16 位读/写除数锁存寄存器的低 8 位, 包含 UART 的波特率除数。如果 UART\_16550\_COMPATIBLE = No, 则仅当 DLAB 位 (LCR[7]) 被设置且 UART 不忙 (即 USR[0] 为 0) 时, 才能访问此寄存器; 否则, 仅仅需 DLAB 位 (LCR[7]) 被设置时, 才能访问此寄存器。

#### 4. 除数锁存寄存器(整数部分高 8 位) (DLH)

偏移地址: 0x0

| DLH | [7:0] | RW |

|-----|-------|----|

|-----|-------|----|

该寄存器构成了一个 16 位读/写除数锁存寄存器的高 8 位，包含 UART 的波特率除数。如果 `UART_16550_COMPATIBLE = No`，则仅当 DLAB 位 (LCR[7]) 被设置且 UART 不忙 (即 USR[0] 为 0) 时，才能访问此寄存器；否则，仅仅需 DLAB 位 (LCR[7]) 被设置时，才能访问此寄存器。

#### 5. 中断使能寄存器(IER)

偏移地址: 0x4

| RW   | #   | #   | RO     | RW    | RW   | RW    | RW    |

|------|-----|-----|--------|-------|------|-------|-------|

| [7]  | [6] | [5] | [4]    | [3]   | [2]  | [1]   | [0]   |

| PTME | 保留  | 保留  | ELCOLR | EDSSI | ELSI | ETBEI | ERBFI |

|      |                                                                                                                           |

|------|---------------------------------------------------------------------------------------------------------------------------|

| bit0 | ERBFI: 启用接收数据可用中断<br>用于启用或禁用接收数据可用中断和字符超时中断的产生（如果处于FIFO模式且FIFO已启用）。属于优先级第二高的中断。<br>0x0: 禁用接收数据中断<br>0x1: 启用接收数据中断         |

| bit1 | ETBEI: 启用发送保持寄存器空中断<br>用于启用或禁用发送保持寄存器空中断的产生。属于优先级第三高的中断。<br>0x0: 禁用发送空中断<br>0x1: 启用发送空中断                                  |

| bit2 | ELSI: 启用接收数据可用中断<br>用于启用或禁用接收数据可用中断的产生，以及字符超时中断的产生（如果处于 FIFO 模式且 FIFO 已启用）。属于优先级第二高的中断。<br>0x0: 禁用接收数据中断<br>0x1: 启用接收数据中断 |

| bit3 | EDSSI: 启用调制解调器状态中断<br>用于启用或禁用调制解调器状态中断的产生。属于优先级第四高的中断。<br>0x0: 禁用调制解调器状态中断<br>0x1: 启用调制解调器状态中断                            |

|      |                                                                                                                                                                                                                        |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit4 | <p>ELCOLR: 中断使能寄存器<br/>用于控制清除LSR寄存器状态的方法。这仅适用于以下状态位：溢出错误（Overrun Error）<br/>奇偶校验错误（Parity Error）帧错误（Framing Error）<br/>中断状态位（Break Interrupt）<br/>仅当LSR_STATUS_CLEAR == Enabled时可写，始终可读。 0x0: 禁用ALC<br/>0x1: 启用ALC</p> |

| bit7 | <p>PTME: 可编程THRE中断模式使能<br/>用于启用或禁用THRE中断的产生。仅当THRE_MODE_USER == Enabled时可写，始终可读。 0x0: 禁用可编程THRE中断模式<br/>0x1: 启用可编程THRE中断模式</p>                                                                                         |

|      |                                                                                                                                                                                                                        |

## 6. 中断识别寄存器(IIR)

偏移地址: 0x8

| RO     | RO    |

|--------|-------|

| [7:6]  | [3:0] |

| FIFOSE | IID   |

|          |                                                                                                                                                                                                            |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit[3:0] | <p>FIFOSE: 用于查看FIFO是否已启用。<br/>0x0: FIFO禁用<br/>0x3: FIFO启用</p>                                                                                                                                              |

| bit[7:6] | <p>IID: 用于查看当前最高优先级的挂起中断类型，具体类型在取值中列出。第3位表示该中断仅在FIFO启用时才会发生，用于区分字符超时条件中断。<br/>0x0: 调制解调器状态中断<br/>0x1: 无挂起中断<br/>0x2: 发送保持寄存器（THR）为空<br/>0x4: 接收数据可用<br/>0x6: 接收器线路状态中断<br/>0x7: 繁忙检测中断<br/>0xC: 字符超时中断</p> |

## 7. FIFO 控制寄存器(FCR)

---

偏移地址: 0x8

| WO    | RW    | WO   | WO     | WO     | WO    |

|-------|-------|------|--------|--------|-------|

| [7:6] | [5:4] | [3]  | [2]    | [1]    | [0]   |

| RT    | TET   | DMAM | XFIFOR | RFIFOR | FIFOE |

|          |                                                                                                                                                                                                       |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit0     | FIFOE: FIFO使能<br>用于启用或禁用发送(XMIT)和接收(RCVR) FIFO。每当该位的值发生变化时，发送和接收FIFO的控制器部分都会被复位。<br>0x0: FIFO禁用<br>0x1: FIFO启用                                                                                        |

| bit1     | RFIFOR: 接收FIFO复位用于复位接收FIFO的控制部分，并将FIFO视为“空”。当选择额外的DMA握手信号(DMA_EXTRA == YES)时，它还会解除DMA RX请求信号和单一信号的断言。注意，该位是“自清除”的，无需手动清除。<br>0x1: 接收FIFO复位                                                            |

| bit2     | XFIFOR: 发送FIFO复位用于复位发送FIFO的控制部分，并将FIFO视为“空”。当选择额外的DMA握手信号(DMA_EXTRA == YES)时，它还会解除DMA TX请求信号和单一信号的断言。注意，该位是“自清除”的，无需手动清除。<br>0x1: 发送FIFO复位                                                            |

| bit3     | DMAM: DMA模式<br>该字段决定了在未选择额外DMA握手信号(DMA_EXTRA == NO)时，dma_tx_req_n和dma_rx_req_n输出信号所使用的DMA信号模式。<br>0x0: 模式0<br>0x1: 模式1                                                                                |

| bit[5:4] | TET: 发送FIFO空触发器<br>当THRE_MODE_USER禁用时，对该字段的写操作无效。该字段用于选择发送FIFO的空阈值电平，当模式激活时，达到该电平时将产生THRE中断。此外，在某些工作模式下，它还决定何时断言dma_tx_req_n信号。<br>0x0: FIFO为空<br>0x1: FIFO中有2个字符<br>0x2: FIFO 1/4满<br>0x3: FIFO 1/2满 |

|          |                                                                                                                                                                                                                           |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit[7:6] | RT: 接收器FIFO触发器<br>用于选择接收FIFO中的触发电平，当达到该电平时将产生接收数据可用中断。<br>在自动流量控制模式下，仅当RTC_FCT禁用时，该字段用于决定何时解除rts_n信号的断言。此外，在某些工作模式下，它还决定何时断言dma_rx_req_n信号。<br>0x0: FIFO中有1个字符<br>0x1: FIFO 1/4满<br>0x2: FIFO 1/2满<br>0x3: FIFO接近满（差2个字符） |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## 8. 线路控制寄存器(LCR)

偏移地址: 0xC

| RW   | RW  | RW  | RW  | RW  | RW   | RW    |

|------|-----|-----|-----|-----|------|-------|

| [7]  | [6] | [5] | [4] | [3] | [2]  | [1:0] |

| DLAB | BC  | SP  | EPS | PEN | STOP | DLS   |

|          |                                                                                                                                                                                                                                                                  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit[1:0] | DLS: 数据长度选择<br>如果UART_16550_COMPATIBLE == NO，则仅在UART空闲（USR[0]为0）时可写；否则，始终可写且始终可读。当LCR_EXT中的DLS_E设置为0时，该寄存器用于选择每个字符传输和接收的数据位数。<br>0x0: 每个字符5个数据位<br>0x1: 每个字符6个数据位<br>0x2: 每个字符7个数据位<br>0x3: 每个字符8个数据位                                                            |

| bit2     | STOP: 停止位数量<br>如果UART_16550_COMPATIBLE == NO，则仅在UART不忙（USR[0]为0）时可写；否则，始终可写且始终可读。该位用于选择每个字符传输和接收的停止位数量。如果设置为0，则传输1个停止位。如果设置为1且数据位为5（LCR[1:0]设置为0），则传输1.5个停止位；否则，传输2个停止位。注意，无论选择多少个停止位，接收器仅检查第一个停止位。<br>0x0: 1个停止位<br>0x1: 当数据长度（LCR[1:0]）为0时，传输1.5个停止位，否则传输2个停止位 |

| bit3     | PEN: 奇偶校验使能<br>如果UART_16550_COMPATIBLE == NO，则仅在UART不忙（USR[0]为0）时可写；否则，始终可写且始终可读。该位用于启用或禁用传输和接收串行字符的奇偶校验生成和检测。<br>0x0: 禁用奇偶校验<br>0x1: 启用奇偶校验                                                                                                                     |

|      |                                                                                                                                                                                                                                                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit4 | <p>EPS: 偶校验选择<br/>如果UART_16550_COMPATIBLE == NO，则仅在UART不忙（USR[0]为0）时可写；否则，始终可写且始终可读。该位用于选择偶校验或奇校验（当PEN设置为1时启用）。如果设置为1，则传输或检查偶数个逻辑“1”；如果设置为0，则传输或检查奇数个逻辑“1”。<br/>0x0: 传输或检查奇校验<br/>0x1: 传输或检查偶校验</p>                                              |

| bit5 | <p>SP: 强制奇偶校验<br/>如果UART_16550_COMPATIBLE == NO，则仅在UART不忙（USR[0]为0）时可写；否则，始终可写且始终可读。该位用于强制奇偶校验值。当PEN、EPS和强制奇偶校验都设置为1时，奇偶校验位将被传输和检查为逻辑0。如果PEN和强制奇偶校验设置为1，而EPS为逻辑0，则奇偶校验位将被传输和检查为逻辑1。如果该位设置为0，则禁用强制奇偶校验。<br/>0x0: 强制奇偶校验 禁用<br/>0x1: 强制奇偶校验 使能</p> |

| bit6 | <p>BC: 断点控制位用于向接收设备发送断点条件。如果设置为1，则串行输出被强制为低电平（逻辑0）状态。当未处于环回模式（由MCR[4]决定）时，sout线将被强制拉低，直到清除断点位。如果启用了SIR模式且处于活动状态（MCR[6]设置为1），则sir_out_n线将连续脉冲输出。在环回模式下，断点条件将内部环回到接收器，并且sir_out_n线被强制拉低。<br/>0x0: 串行输出释放用于数据传输<br/>0x1: 串行输出被强制为低电平状态</p>          |

| bit7 | <p>DLAB: 除数锁存器访问位如果UART_16550_COMPATIBLE == NO，则仅在UART不忙（USR[0]为0）时可写；否则，始终可写且始终可读。该位用于启用对除数锁存寄存器（DLL和DLH/LPDLL和LPDLH）的读写操作，以设置UART的波特率。在初始波特率设置完成后，必须清除该位，才能访问其他寄存器。<br/>0x0: 仅在UART不忙时，除数锁存寄存器可写<br/>0x1: 除数锁存寄存器始终可读可写</p>                    |

## 9. 调制解调寄存器(MCR)

偏移地址: 0x10

| RW   | RW       | RW   | RW   | RW  | RW  |

|------|----------|------|------|-----|-----|

| [5]  | [4]      | [3]  | [2]  | [1] | [0] |

| AFCE | LoopBack | OUT2 | OUT1 | RTS | DTR |

|      |                                                                                                                                                                                                                                                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit0 | <p>DTR: 数据就绪控制<br/>用于直接控制数据终端就绪 (dtr_n) 输出。该输出用于通知调制解调器或数据集, UART已准备好建立通信。<br/>注意, 在环回模式下 (MCR[4]设置为1), dtr_n输出将被保持在非活动高电平, 而该位置的值将被内部环回到输入。<br/>0x0: dtr_n 解除有效 (逻辑 1)<br/>0x1: dtr_n 有效 (逻辑 0)</p>                                                                                               |

| bit1 | <p>RTS: 请求发送 (RTS) 控制直接控制 RTS 输出信号:<br/>非自动流控: MCR[1]=1 时 rts_n=0<br/>自动流控: rts_n 受接收 FIFO 阈值门控 (高于阈值时 rts_n=1)<br/>0x0: rts_n 解除有效 (逻辑 1)<br/>0x1: rts_n 有效 (逻辑 0)</p>                                                                                                                            |

| bit2 | <p>OUT1: 用户指定的Output1 (out1_n) 输出控制<br/>用于直接控制用户指定的Output1 (out1_n) 输出。写入该位置的值将被反转并输出到 out1_n。注意, 在环回模式下 (MCR[4]设置为1), out1_n输出将被保持在非活动高电平, 而该位置的值将被内部环回到输入。<br/>0x0: out1_n 解除有效 (逻辑 1)<br/>0x1: out1_n 有效 (逻辑 0)</p>                                                                             |

| bit3 | <p>OUT2: 用户指定的Output2 (out2_n) 输出控制<br/>用于直接控制用户指定的Output2 (out2_n) 输出。写入该位置的值将被反转并输出到 out2_n。注意, 在环回模式下 (MCR[4]设置为1), out2_n输出将被保持在非活动高电平, 而该位置的值将被内部环回到输入。<br/>0x0: out2_n 解除有效 (逻辑 1)<br/>0x1: out2_n 有效 (逻辑 0)</p>                                                                             |

| bit4 | <p>LoopBack: 回环模式使能<br/>用于将UART置于诊断模式, 以便进行测试。如果在UART模式下运行 (SIR_MODE != Enabled 或未激活, 即MCR[6]设置为0), sout线上的数据将被拉高, 而串行数据输出将被内部环回到sin线。在这种模式下, 所有中断功能正常。此外, 在环回模式 下, 调制解调器控制输入 (dsr_n、cts_n、ri_n、dcd_n) 将被断开, 而调制解调器控制输出 (dtr_n、rts_n、out1_n、out2_n) 将被内部环回到输入。<br/>0x0: 环回模式禁用<br/>0x1: 环回模式启用</p> |

| bit5 | <p>AFCE: 自动控制流使能<br/>仅当 AFCE_MODE == Enabled 时可写, 始终可读。当 FIFO 使能且 AFCE 置位时, 自动流控功能激活。<br/>0x0: 自动流控禁用<br/>0x1: 自动流控使能</p>                                                                                                                                                                          |

## 10. 线路状态寄存器(LSR)

偏移地址：0x14

| RO        | RO  | RO   | RO   | RO  | RO  | RO  | RO  | RO  |